1 偶数分频

(1)2的幂分频

案例I 二分频

i: div_2.v

module div_2(

input i_clk,

input i_rst_n,

output o_clk

);

reg [0:0] cnt;

always @ (posedge i_clk, negedge i_rst_n)

if (!i_rst_n)

cnt <= 0;

else

cnt <= cnt + 1'b1;

assign o_clk = cnt[0];

endmodule

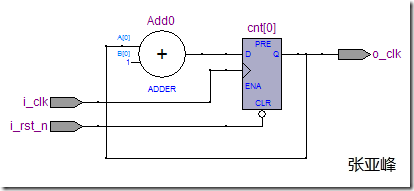

ii:RTL视图(QII综合结果)

图1 二分频的RTL视图

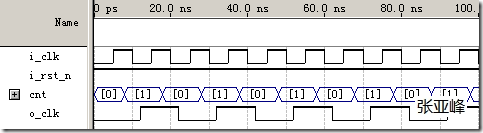

iii:仿真波形(QII仿真结果)

图2 二分频的仿真波形

案例II 四分频

i:div_4.v

module div_4(

input i_clk,

input i_rst_n,

output o_clk

);

reg [1:0] cnt;

always @ (posedge i_clk, negedge i_rst_n)

if (!i_rst_n)

cnt <= 0;

else

cnt <= cnt + 1'b1;

assign o_clk = cnt[1];

endmodule

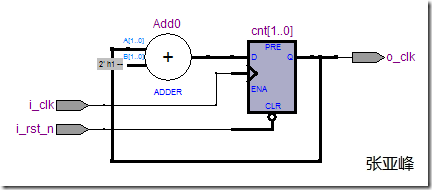

ii:RTL视图(QII综合结果)

图3 四分频的RTL视图

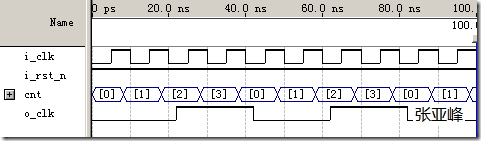

iii:仿真波形(QII仿真结果)

图4 四分频的仿真波形

(2)不是2的幂分频

案例I 六分频

i:div_6.v

module div_6(

input i_clk,

input i_rst_n,

output reg o_clk

);

// log2(6) = 2.5850 <= 3

reg [2:0] cnt;

// 6 bit counter: 0 ~ 5

// 5 = 6 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt <= 0;

else

begin

if (cnt == 5)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

end

// 0 ~ 2 -> 1

// 2 ~ 5 -> 0

// 2 = 6>>1 - 1

// 5 = 6 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk <= 0;

else

begin

if (cnt <= 2)

o_clk <= 1;

else

o_clk <= 0;

end

end

endmodule

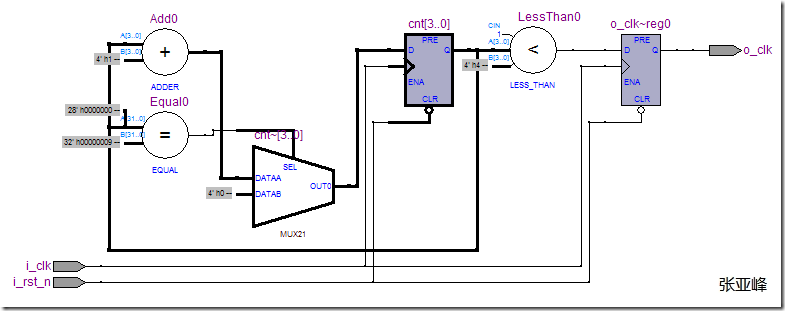

ii:RTL视图(QII综合结果)

图5 六分频的RTL视图

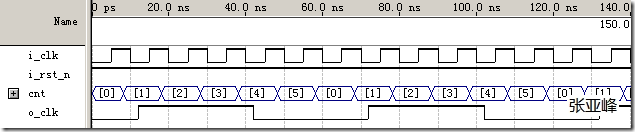

gt;iii:仿真波形(QII仿真结果)

图6 六分频的仿真波形

案例II 十分频

i:div_10.v

module div_10(

input i_clk,

input i_rst_n,

output reg o_clk

);

// log2(10) = 3.3219 <= 4

reg [3:0] cnt;

// 10 bit counter: 0 ~ 9

// 9 = 10 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt <= 0;

else

begin

if (cnt == 9)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

end

// 0 ~ 4 -> 1

// 4 ~ 9 -> 0

// 4 = 10>>1 - 1

// 9 = 10 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk <= 0;

else

begin

if (cnt <= 4)

o_clk <= 1;

else

o_clk <= 0;

end

end

endmodule

ii:RTL视图(QII综合结果)

图7 十分频的RTL视图

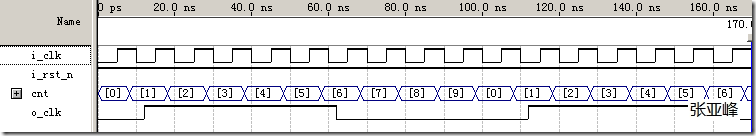

iii:仿真波形(QII仿真结果)

图8 十分频的仿真波形

2 奇数分频

案例I 三分频

i. div_3.v

module div_3(

input i_clk,

input i_rst_n,

output o_clk

);

// log2(3) = 1.5850 <= 2

reg [1:0] cnt_p; // 上升沿计数子

// 3位上升沿计数器: 0 ~ 2

// 2 = 3 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt_p <= 0;

else

begin

if (cnt_p == 2)

cnt_p <= 0;

else

cnt_p <= cnt_p + 1'b1;

end

end

// log2(3) = 1.5850 <= 2

reg [1:0] cnt_n; // 下降沿计数子

// 3位下降沿计数器: 0 ~ 2

// 2 = 3 - 1

always @ (negedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt_n <= 0;

else

begin

if (cnt_n == 2)

cnt_n <= 0;

else

cnt_n <= cnt_n + 1'b1;

end

end

reg o_clk_p; // 上升沿时钟输出寄存器

// 输出上升沿时钟

// 0 ~ 1 ↑-> 1

// (1+1) ~ 2 ↑-> 0

// 1 = 3>>1

// 2 = 3 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk_p <= 0;

else

begin

if (cnt_p <= 1) // 1 = 3>>1

o_clk_p <= 1;

else

o_clk_p <= 0;

end

end

reg o_clk_n; // 下降沿时钟输出寄存器

// 输出下降沿时钟

// 0 ~ 1 ↓-> 1

// (1+1) ~ 2 ↓-> 0

// 1 = 3>>1

// 2 = 3 - 1

always @ (negedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk_n <= 0;

else

begin

if (cnt_n <= 1) // 1 = 3>>1

o_clk_n <= 1;

else

o_clk_n <= 0;

end

end

assign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码)

endmodule

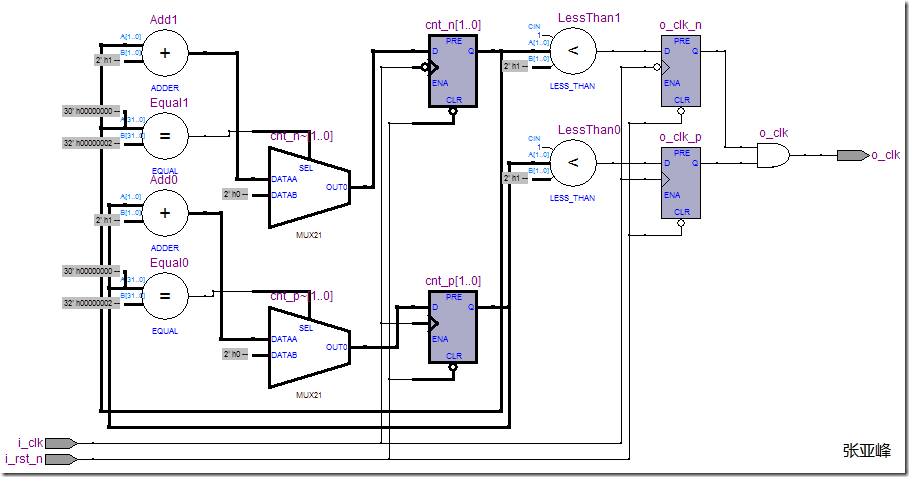

ii:RTL视图(QII综合结果)

图9 三分频的RTL视图

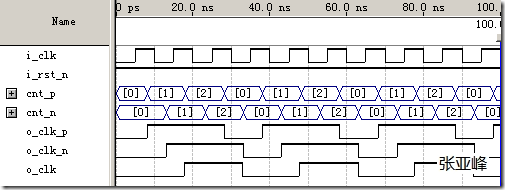

iii:仿真波形(QII仿真结果)

图10 三分频的仿真波形

案例II 五分频

i. div_5.v

module div_5(

input i_clk,

input i_rst_n,

output o_clk

);

// log2(5) = 2.3219 <= 3

reg [2:0] cnt_p; // 上升沿计数子

// 5位上升沿计数器: 0 ~ 4

// 4 = 5 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt_p <= 0;

else

begin

if (cnt_p == 4)

cnt_p <= 0;

else

cnt_p <= cnt_p + 1'b1;

end

end

// log2(5) = 2.3219 <= 3

reg [2:0] cnt_n; // 下降沿计数子

// 5位下降沿计数器: 0 ~ 4

// 4 = 5 - 1

always @ (negedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

cnt_n <= 0;

else

begin

if (cnt_n == 4)

cnt_n <= 0;

else

cnt_n <= cnt_n + 1'b1;

end

end

reg o_clk_p; // 上升沿时钟输出寄存器

// 输出上升沿时钟

// 0 ~ 2 ↑-> 1

// (2+1) ~ 4 ↑-> 0

// 2 = 5>>1

// 4 = 5 - 1

always @ (posedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk_p <= 0;

else

begin

if (cnt_p <= 2) // 2 = 5>>1

o_clk_p <= 1;

else

o_clk_p <= 0;

end

end

reg o_clk_n; // 下降沿时钟输出寄存器

// 输出下降沿时钟

// 0 ~ 2 ↓-> 1

// (2+1) ~ 4 ↓-> 0

// 2 = 5>>1

// 4 = 5 - 1

always @ (negedge i_clk, negedge i_rst_n)

begin

if (!i_rst_n)

o_clk_n <= 0;

else

begin

if (cnt_n <= 2) // 2 = 5>>1

o_clk_n <= 1;

else

o_clk_n <= 0;

end

end

assign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码)

endmodule

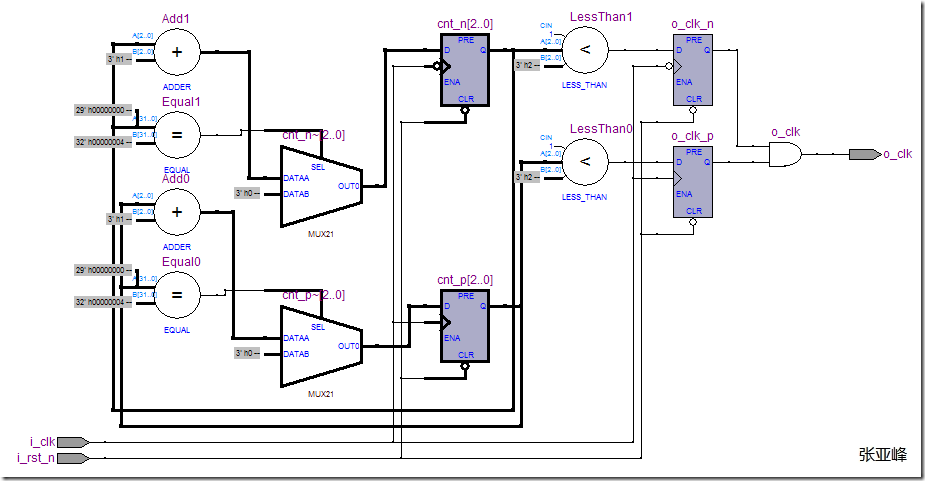

ii:RTL视图(QII综合结果)

图11 五分频的RTL视图

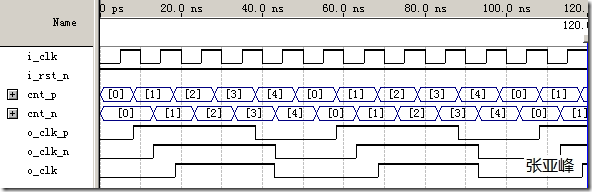

iii:仿真波形(QII仿真结果)

图12 五分频的仿真波形

参考资料

1. 真 OO無雙,(原創) 如何設計除頻器? (SOC) (Verilog) (MegaCore)

http://www.cnblogs.com/oomusou/archive/2008/07/31/verilog_clock_divider.html

2. 小時不識月,N倍奇数分频器.(Verilog)

http://blog.ednchina.com/2006tx_yafeng/146438/message.aspx

3. 小時不識月,N倍偶数分频器.(Verilog)