ROM是一种重要的时序逻辑存储电路,它的逻辑功能是在地址信号的选择下,从指定存储单元中读取相应的数据。R0M只能进行数据的读取,而不能修改或写人新的数据,本节将以16×8的ROM为例,介绍ROM的设计方法。

Verilog HDL:

1 module ROM_ex1 (addr, data, en); 2 3 input [3:0] addr;//地址选择信号 4 input en; //使能端 5 output reg [7:0] data;//数据输出端 6 reg[7:0] data1 [15:0]; 7 8 always @(*) 9 begin 10 data1[0] <= 8'b1010_1001; 11 data1[1] <= 8'b1111_1101; 12 data1[2] <= 8'b1110_1001; 13 data1[3] <= 8'b1101_1100; 14 data1[4] <= 8'b1011_1001; 15 data1[5] <= 8'b1100_0010; 16 data1[6] <= 8'b1100_0101; 17 data1[7] <= 8'b0000_0100; 18 data1[8] <= 8'b1110_1100; 19 data1[9] <= 8'b1000_1010; 20 data1[10] <= 8'b1100_1111; 21 data1[12] <= 8'b1100_0001; 22 data1[13] <= 8'b1001_1111; 23 data1[14] <= 8'b1010_0101; 24 data1[15] <= 8'b0101_1100; 25 if (en) 26 begin 27 data[7:0] <= data1[addr]; 28 end 29 else 30 begin 31 data[7:0] <= 8'bzzzz_zzzz; 32 end 33 end 34 35 endmodule

Testbench:

1 `timescale 1 ps/ 1 ps 2 module ROM_ex1_vlg_tst(); 3 reg [3:0] addr; 4 reg en; 5 wire [7:0] data; 6 7 ROM_ex1 i1 ( 8 .addr(addr), 9 .data(data), 10 .en(en) 11 ); 12 initial 13 begin 14 addr = 4'd0; 15 en = 1'b0; 16 #10 addr = 4'd5; 17 en = 1'b1; 18 #10 addr = 4'd9; 19 #10 addr = 4'd12; 20 #10 addr = 4'd15; 21 $display("Running testbench"); 22 end 23 24 endmodule

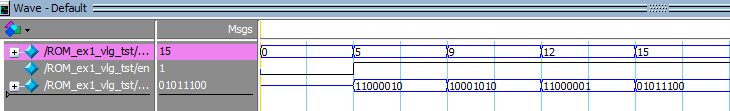

仿真波形:

观察波形可知,当 en 为“1”时,data 输出数据,否则 data 为高阻态,addr 为地址选择信号,当其输入不同的值时,data 输出相应的存储的数据。