if语句法

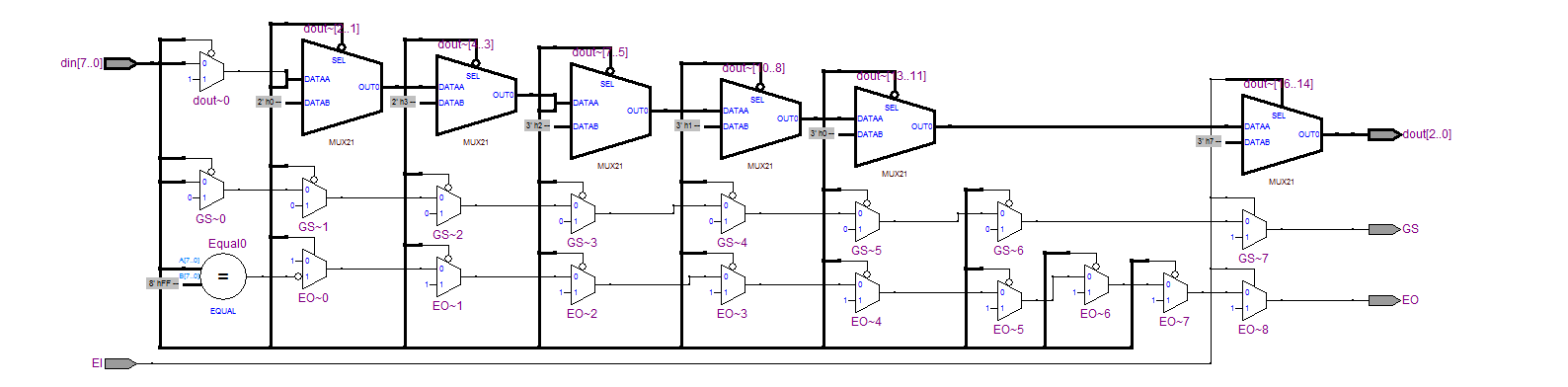

1 //8线-3线优先编码器设计(74LS148) 2 // 3 //EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO 4 //0 | 0 x x x x x x x | 0 0 0 0 1 5 //0 | 1 0 x x x x x x | 0 0 1 0 1 6 //0 | 1 1 0 x x x x x | 0 1 0 0 1 7 //0 | 1 1 1 0 x x x x | 0 1 1 0 1 8 //0 | 1 1 1 1 0 x x x | 1 0 0 0 1 9 //0 | 1 1 1 1 1 0 x x | 1 0 1 0 1 10 //0 | 1 1 1 1 1 1 0 x | 1 1 0 0 1 11 //0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 1 12 //0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 0 13 //1 | x x x x x x x x | 1 1 1 1 1 14 15 16 module encoder_83 (din, EI, GS, EO, dout); 17 input [7:0] din; //编码输入端data_in,低电平有效 18 input EI; //使能输入端EI(选通输入端),EI为 0 时芯片工作,即允许编码 19 output [2:0] dout; //编码输出端data_out 20 output GS; //片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效 21 output EO; //使能输出端EO(选通输出端) 22 reg [2:0] dout; 23 reg GS, EO; 24 always @(din or EI) 25 if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在高电平 26 else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; end 27 else if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; end 28 else if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; end 29 else if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; end 30 else if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; end 31 else if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; end 32 else if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; end 33 else if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; end 34 else if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end //芯片工作,但无编码输入 35 else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch) 36 endmodule 37 38 //EI = 0 表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作) 39 //EO = 0 表示电路工作,但无编码输入(用于级联) 40 //GS = 0 表示电路工作,且有编码输入(判断输入端是否有输入)

testbench:

1 `timescale 1 ps/ 1 ps 2 module encoder_83_vlg_tst(); 3 reg EI; 4 reg [7:0] din; 5 wire EO; 6 wire GS; 7 wire [2:0] dout; 8 encoder_83 i1 (.EI(EI), .EO(EO), .GS(GS), .din(din), .dout(dout)); 9 initial 10 begin 11 EI = 1; 12 din = 8'b11111111; 13 #10 EI = 0; 14 #10 din = 8'b01010101; 15 #10 din = 8'b10101010; 16 #10 din = 8'b11010101; 17 #10 din = 8'b11101010; 18 #10 din = 8'b11110101; 19 #10 din = 8'b11111010; 20 #10 din = 8'b11111101; 21 #10 din = 8'b11111110; 22 #10 din = 8'b11111111; 23 end 24 endmodule

case语句法

1 //8线-3线优先编码器设计(74LS148) 2 // 3 //EI | A7 A6 A5 A4 A3 A2 A1 A0 | Y2 Y1 Y0 GS EO 4 //0 | 0 x x x x x x x | 0 0 0 0 1 5 //0 | 1 0 x x x x x x | 0 0 1 0 1 6 //0 | 1 1 0 x x x x x | 0 1 0 0 1 7 //0 | 1 1 1 0 x x x x | 0 1 1 0 1 8 //0 | 1 1 1 1 0 x x x | 1 0 0 0 1 9 //0 | 1 1 1 1 1 0 x x | 1 0 1 0 1 10 //0 | 1 1 1 1 1 1 0 x | 1 1 0 0 1 11 //0 | 1 1 1 1 1 1 1 0 | 1 1 1 0 1 12 //0 | 1 1 1 1 1 1 1 1 | 1 1 1 1 0 13 //1 | x x x x x x x x | 1 1 1 1 1 14 15 16 module encoder_83_case (din, EI, GS, EO, dout); 17 input [7:0] din; //编码输入端data_in,低电平有效 18 input EI; //使能输入端EI(选通输入端),EI为 0 时芯片工作,即允许编码 19 output [2:0] dout; //编码输出端data_out 20 output GS; //片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效 21 output EO; //使能输出端EO(选通输出端) 22 reg [2:0] dout; 23 reg GS, EO; 24 always @(din or EI) 25 if(EI) 26 begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在高电平 27 else 28 casez (din) //建议用casez语句,casez把z/?匹配成任意。 casex把z/?/x匹配成任意,x为仿真初态 29 8'b0??????? : begin dout <= 3'b000; GS <= 0; EO <= 1; end //无关项建议用?表示,?是高阻态的另一种表示。?,z,Z是等价的 30 8'b10?????? : begin dout <= 3'b001; GS <= 0; EO <= 1; end 31 8'b110????? : begin dout <= 3'b010; GS <= 0; EO <= 1; end 32 8'b1110???? : begin dout <= 3'b011; GS <= 0; EO <= 1; end 33 8'b11110??? : begin dout <= 3'b100; GS <= 0; EO <= 1; end 34 8'b111110?? : begin dout <= 3'b101; GS <= 0; EO <= 1; end 35 8'b1111110? : begin dout <= 3'b110; GS <= 0; EO <= 1; end 36 8'b11111110 : begin dout <= 3'b111; GS <= 0; EO <= 1; end 37 8'b11111111 : begin dout <= 3'b111; GS <= 1; EO <= 0; end //芯片工作,但无编码输入 38 default : begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch) 39 endcase 40 endmodule 41 42 //EI = 0 表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作) 43 //EO = 0 表示电路工作,但无编码输入(用于级联) 44 //GS = 0 表示电路工作,且有编码输入(判断输入端是否有输入)

如有错误还请指出,如有侵权还请告知,如需转载请注明出处!