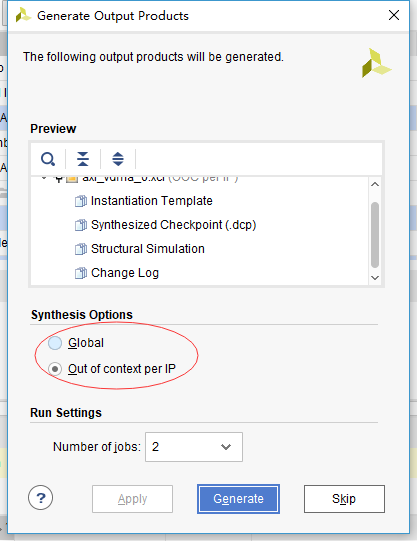

在Vivado定制IP的时候,或者在IP Catalog中双击一个IP,不论该IP是我们自己添加到工程的自定义IP,还是Vivado自己带的IP,选择"Customize IP"后都会弹出如下图所示的框框。可以看到一种叫做”Global”,一种叫”Out of Context (OOC)”。

Global 即全局

如果选择的是全局综合选项,那IP生成的文件将会和其他的用户文件一起进行综合,这也就意味着,每一次用户文件被修改后,源码级IP都会跟着一起综合一遍。

Out-Of-Context (OOC) 即脱离上下文

OOC选项是Vivado给我们的默认选项,在OOC模式下,Vivado将会把生成的IP当成一个单独的模块来进行综合,生成.dcp (design checkpoint)文件,工程要用到IP的时候,只需从.dcp文件中解析出对应IP的网表文件即可,而不需对IP进行重新综合,这样的方式可以加快综合的速度;而Gobal选择则是每次工程综合的时候,IP核都会和工程一起综合,综合时间很长,也不会产生.dcp文件。OOC同时会使用一个只在OOC模式下有用的约束文件“_ooc.xdc”。 除了生成.dcp文件,OOC还会生成一个以”stub.v”结尾的HDL文件,是当前IP设计的一个黑盒文件,只有输入输出端口,工程调用这个的时候实际上是在解析.dcp中的网表文件,进而继续综合和布局布线。

OOC的优势

通过综合实现某个模块的快速迭代,不用综合系统的其余部分,整个设计的迭代更快了;

利于系统其余部分的快速迭代,如果某部分确定稳定不变了,可以对这个模块进行OOC综合操作,保留这个综合版本,这样就可以方便迭代其余部分;

OOC将会产生”_sim_netlist.v” 或者 “_sim_netlist.vhdl”仿真文件,如果我们在使用只支持某种语言的仿真器,而IP不提供该语言的RTL文件,我们就可以直接用这些仿真文件进行IP仿真。

关于高阻态和OOC(out of context)综合方式

如果设计中存在三态(高阻态),OOC综合操作就会受到影响,FPGA仅支持I/O输出端口的高阻态,在器件内部是不允许的,如果你使用OOC综合方式,Vivado工具并不知道某个具体的信号是连接I/O输出还是在器件内部进行连接,最后,综合工具会将这个高阻信号转换为某个逻辑值,而不是最为高阻态进行综合。

举个例子,下面的代码就会带来不好的影响:

assign my_signal = enable?din1:1’bz;

通过OOC方式综合后,my_signal信号值就不会是高阻值Z了, Vivado会选择不保留三态。如果my_signal信号只连接到外部输出I/O呢?即能够使用OOC方式对这部分模块进行综合,同时保留三态。

满足上述需求的方式就是在RTL中实例化一个三态缓存(buffer)。

OBUF u1(.l(din1), .T(n_enable), .O(my_signal));

参考:

http://www.sohu.com/a/129575422_292853 关于高阻态和OOC(out of context)综合方式