存储器组织

随机访问存储器RAM

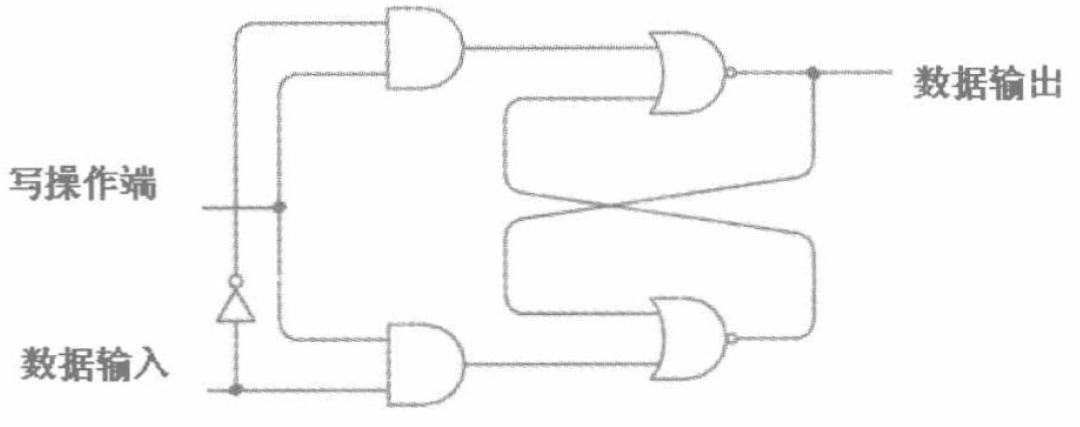

之前我们讨论过D型电平触发器,它可以保存1位信息,将数据端命名为数据输入,将时钟输入命名为写操作端,将两个Q命名为数据输出:

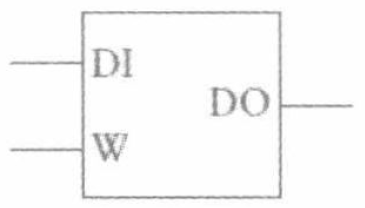

这个电路和之前的电路是同一种触发器,只是命名的方式不同。保存输入的方式就是将写操作端从0置为1,因为存储进去的数据好像被锁住,故该电路也被称为锁存器,锁存器也可以用下列符号表示:

可以将多个锁存器相连,同时存储多位数据:

这就是8位锁存器,输入和输出各有8个,写操作端在非工作状态下为0,如果要存储数据,首先要把写操作端置为1。然后再置0。这个8位锁存器也可以用下列符号表示:

这个8位锁存器的输入有8位,假设我们想制作一个这样的锁存器:它只有一个数据输入端和一个数据输出端,而不是8个,每次指定该数据存储到某一个单个锁存器中,8个锁存器可以独立的存储,我们还想要通过观察输出信号端确定实际的8位输出。

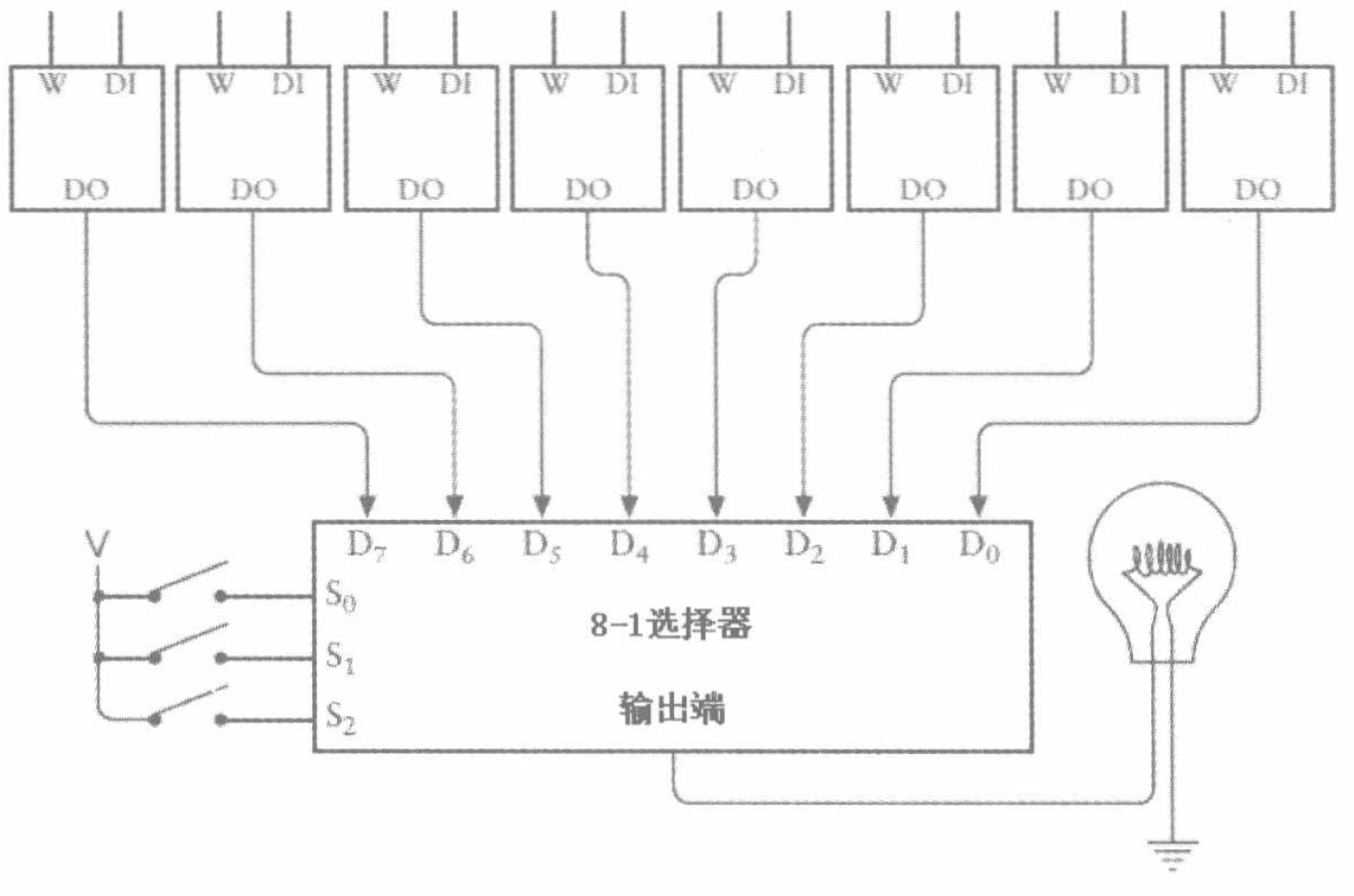

假设我们有一个灯泡,面对8位输出端的时候,如何才能确定存储的数字是什么?最简单的方法就是拿着灯泡依次连接输出端,但是那样太麻烦了,我们需要更自动化的方法检查,可以设置多个开关,根据开关的不同组合来将对应位的信号输出到灯泡:

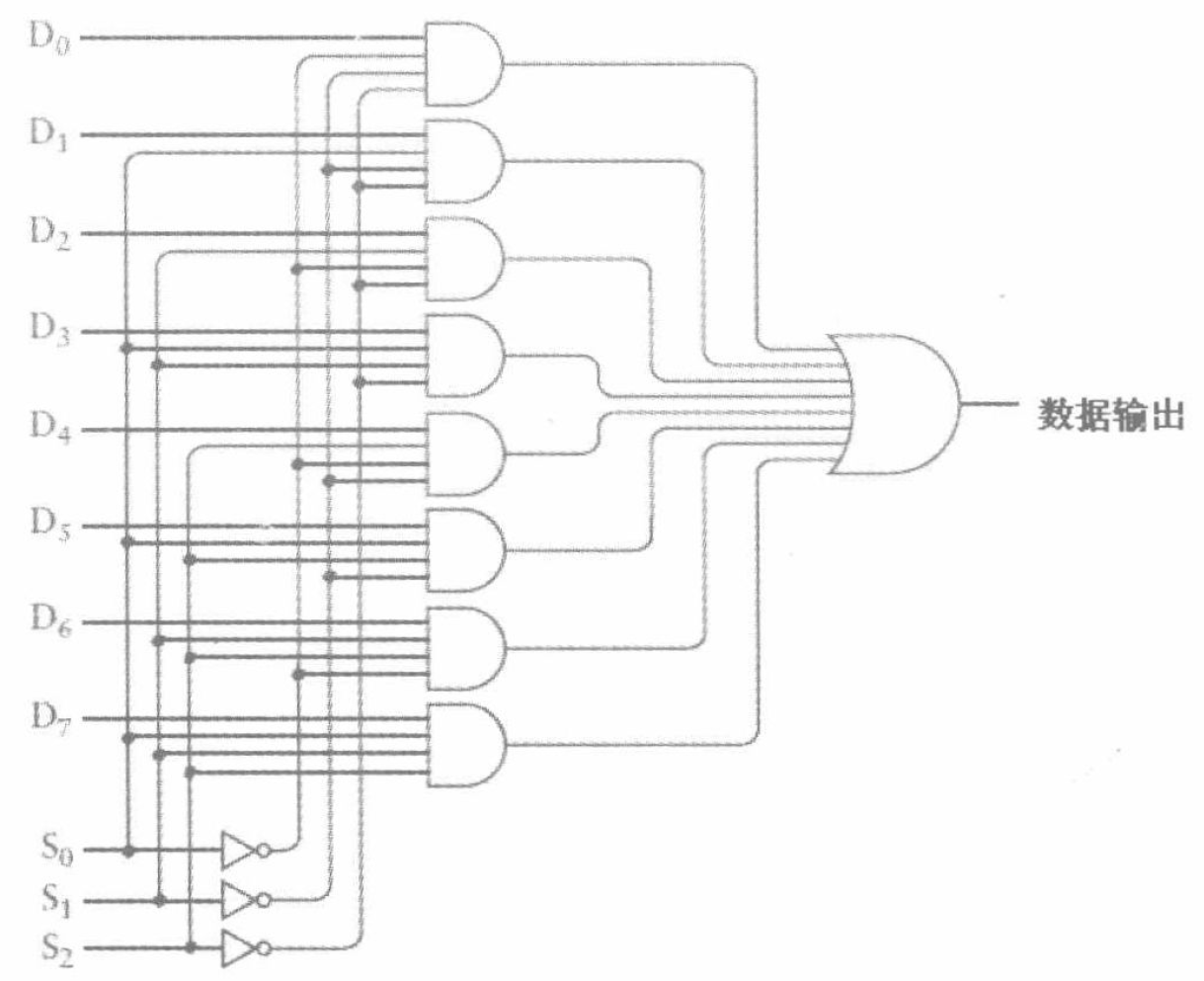

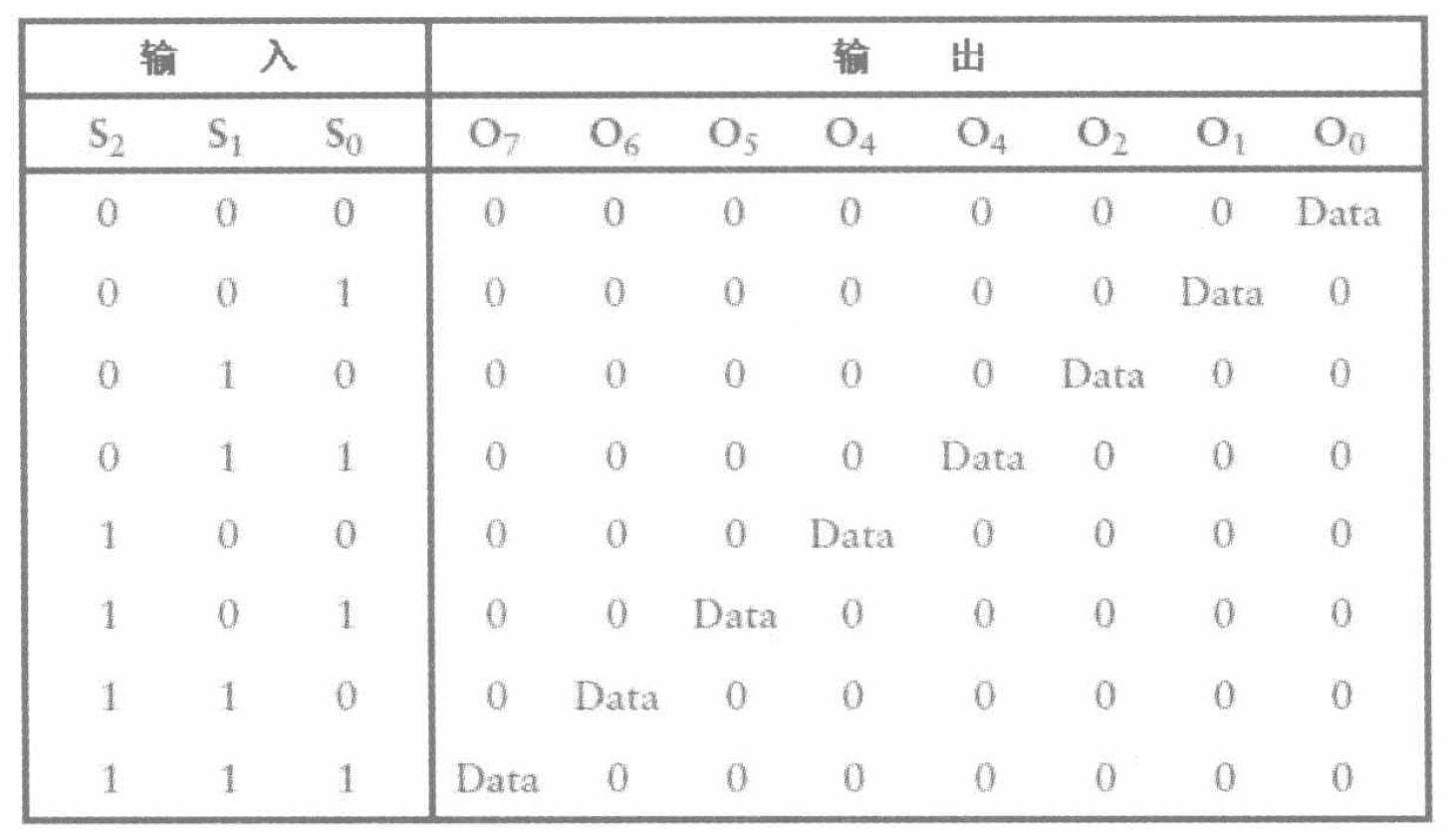

这三个开关可以组成一个三位二进制数字,正好可以表示8位,根据不同的开关情况来让对应位的输出连接到灯泡,这个8-1选择器的结构如下:

它由三个反向器、八个4端口输入与门和一个8端口输入或门组成,真值表如下:

至此,输出端已经完成了检查的功能,那么怎么让输入端指定存储到某一个锁存器中呢?

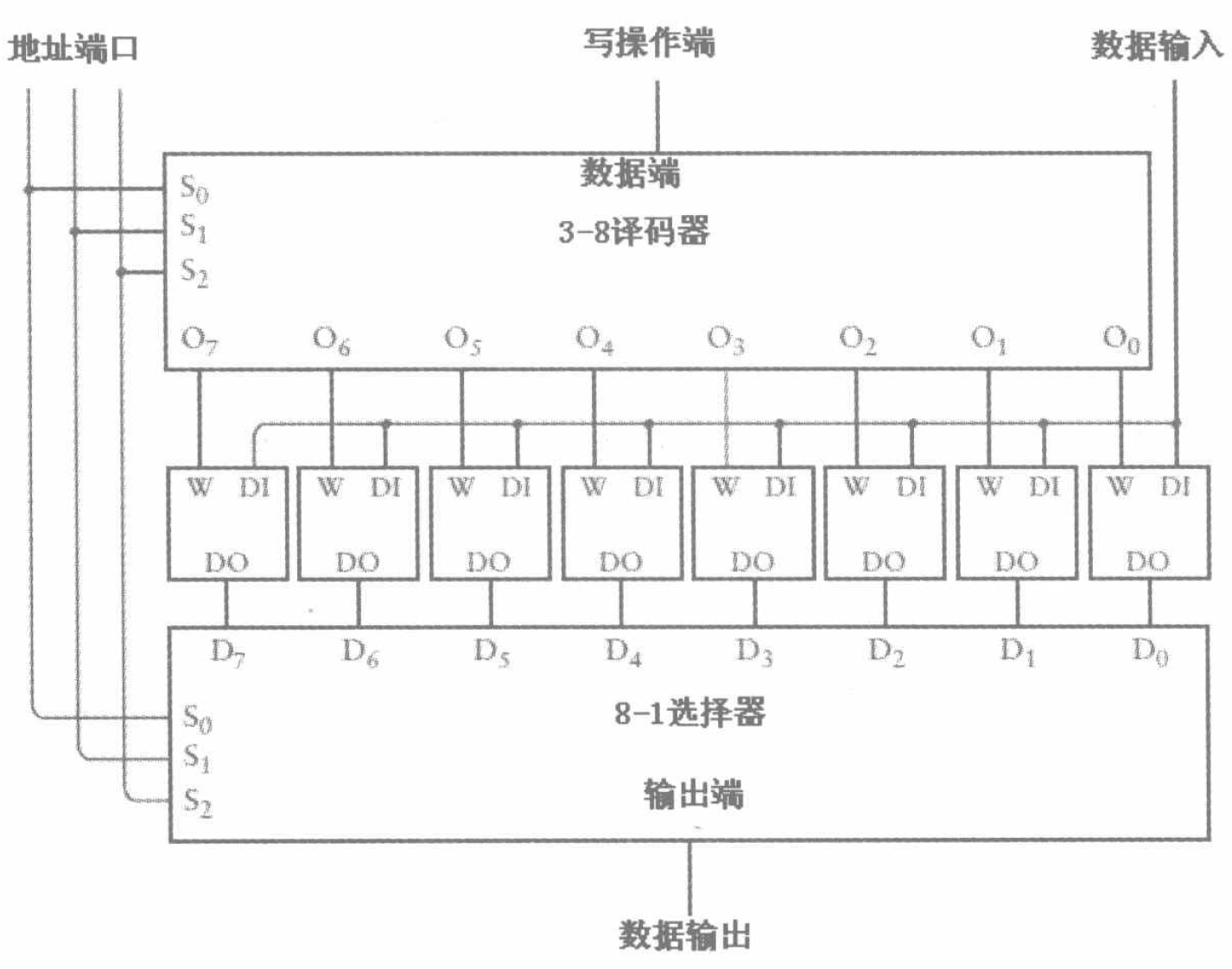

可以用如下系统来完成:

对于整个系统而言,起选择作用的三个信号被称为地址端口,也就是查看8位当中的哪一个地址,译码器负责将输入输出到对应锁存器,选择器负责将对应锁存器中的值输出出来。

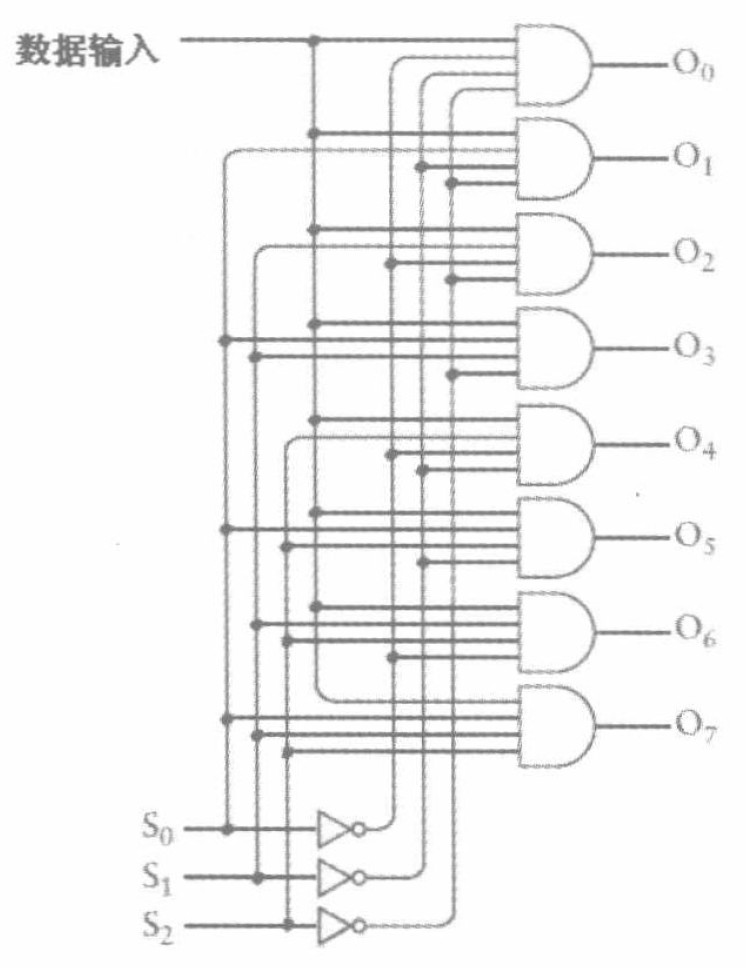

3-8译码器是一个和选择器作用相反的电路元件,3-8的意思是输出端口有8个,而选择的开关有3个,结构如下:

它的功能就是根据不同的S1、S2、S3组合将数据输入到8个不同的输出端,真值表如下:

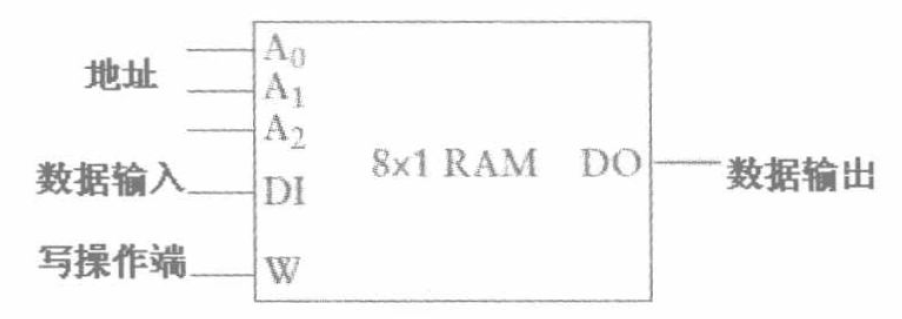

这个系统被称为读/写存储器,或随机访问存储器,也就是RAM(Random Access Memory),可以用下列符号表示:

这种存储器不仅可以在每个锁存器中存储新数据,还可以检查每个锁存器都保存了什么数据,只需要改变地址及数据输入,就能完成读写功能。因为可以读取任意一个锁存器的数据,无需顺序访问,因此被称为随机访问存储器。

需要注意的是,RAM对数据的存储是依赖电流的,内部类似继电器属性的元件必须依靠电流才能维持电路的结构,如果断掉电源,内部的所有元件都还原到未触发状态,数据就会消失,所以随机访问存储器又被称为易失性(volatile)存储器。

RAM阵列

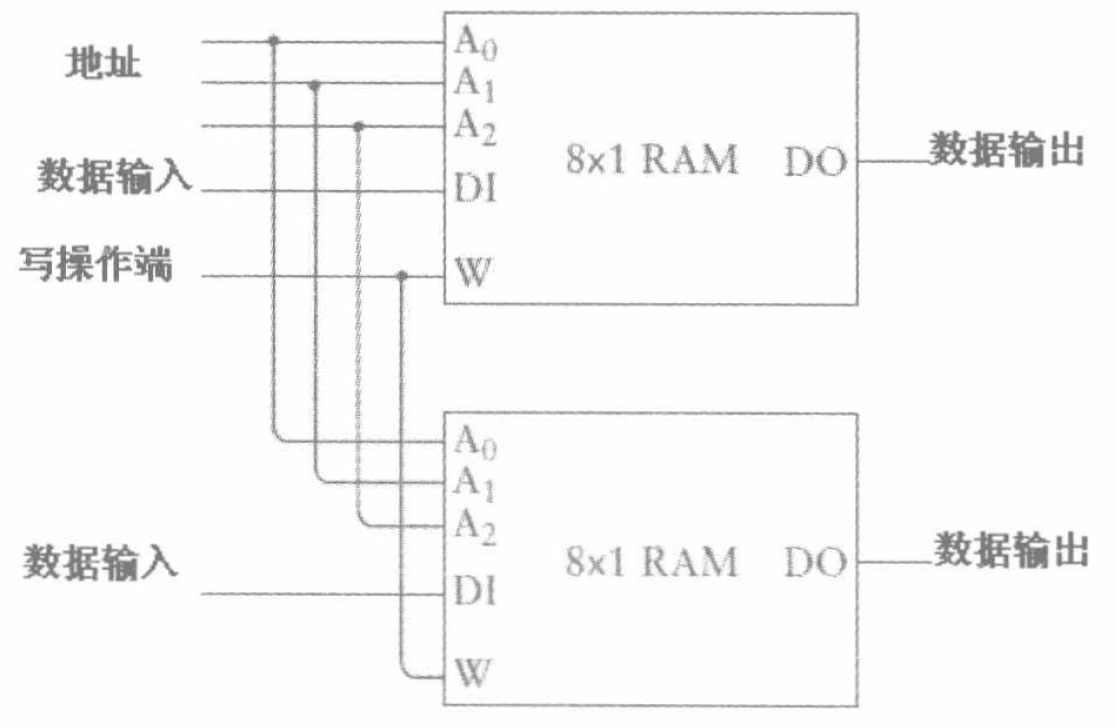

我们可以通过共享地址的方式把两个8*1的RAM阵列连接起来:

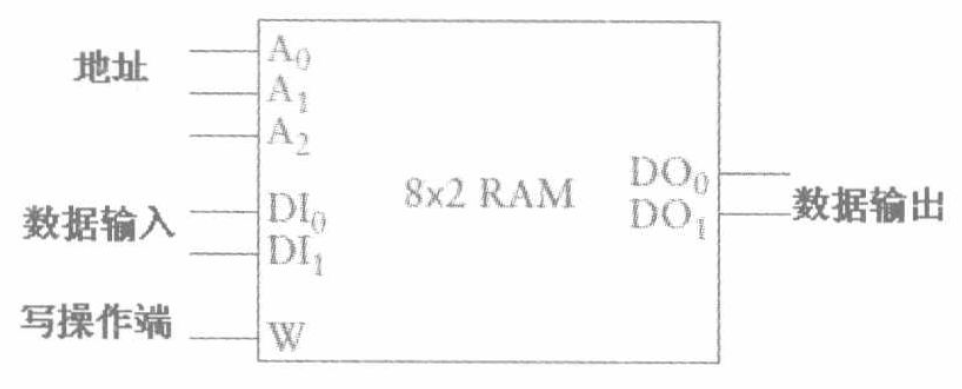

不同的数据输入可以存储到相同的地址,相当于原来可以存8个1位的二进制数,现在变成了可以存8个2位的二进制数,这样就得到了一个8*2的RAM阵列:

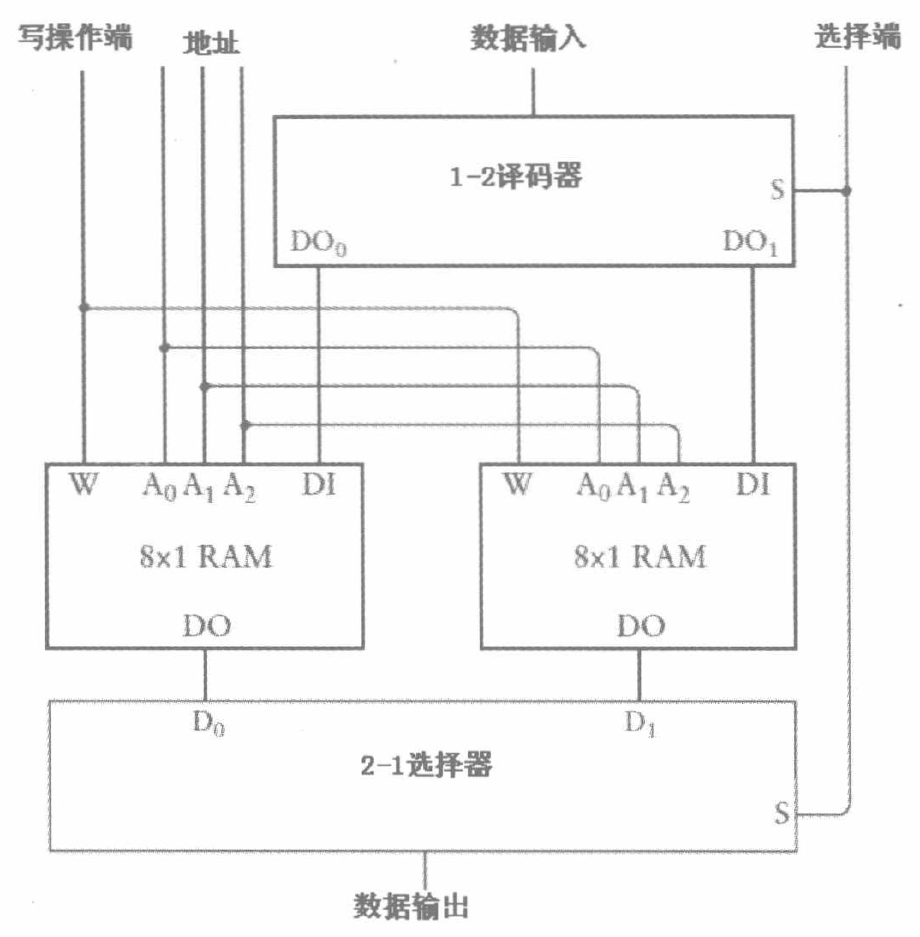

RAM阵列还可以用多个锁存器搭配选择器和译码器来组合,用之前的组成RAM的原理:

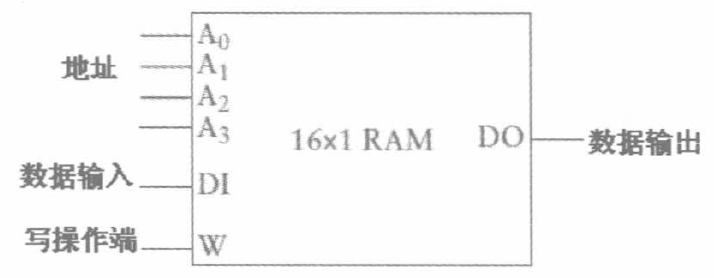

这里多了一个选择端,用来选择数据输入到哪一个锁存器,以及数据输出的数据来自于哪个锁存器,相当于进一步扩大了地址范围,选择端本质上扮演了第4根地址线的角色,因此这种结构本质上是一个16*1的RAM阵列:

它可以存储16个单位,每个单位占1位。

RAM阵列的存储容量与其地址输入端的数量有关,它们的关系如下:

$$

RAM阵列的存储容量=2^{地址输入端的个数}

$$

大规模的RAM阵列可以存储更多的位,之所以存储容量1024byte=1KB,是因为这其中的二次幂关系,一个RAM阵列有10个地址输入端,它就有1KB的存储容量。

用控制面板操作存储器

假设现在已经构造好了一个64KB的RAM阵列(16个地址位代表可以存65535组数据,一组是8bit,相当于1字节,共64KB)

要构造的控制面板如下:

最上面16个开关用于控制地址位,下面8个开关是控制要输入的8bit数据,8个灯泡用来显示8位数据。写操作端为1时代表将数据写入对应地址。控制端为0时代表控制面板失去对存储器的控制,此时该存储器连接其他电路,其他电路可以取用该存储器中的数据;控制端为1时代表控制面板可以控制存储器了。

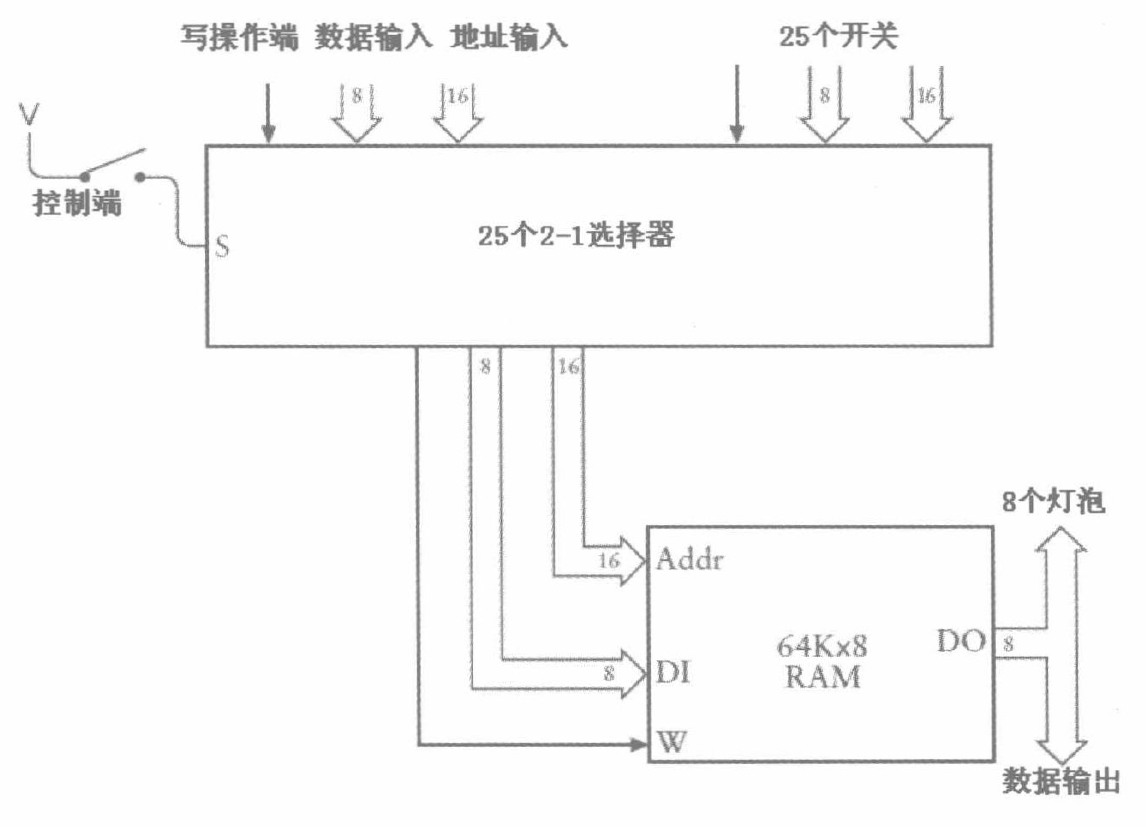

我们需要25个2-1选择器来完成功能(2-1选择器有2个输入1个输出),其中包括16个地址输入端、8个数据输入端以及1个写操作端,电路如下:

当控制端断开时,25个2-1选择器都会选择左上角的外部信号,此时外部信号操作存储器;当控制端闭合时,此时25个2-1选择器都会选择右上角的开关发出的信号。

控制面板控制存储区既实现了数据的输入和读取,又给其他部件提供了接入系统的机会。