工具支持的三种testbench:

- MAX Testbench (通过stil2verilog将STIL pattern转换为Verilog simulation testbench)

- Verilog DPV Testbench (Verilog Testbench 将测试激励应用于DUT,并根据数据文件中指定的预期数据检查响应)

- Legacy Verilog Testbench (Not recommanded)

一、MAX Testbench

- 没有Verilog PLL——更快的仿真运行时间

- 降低内存使用量

- 简化仿真调试

- 可以为测试平台生成Verilog仿真脚本

- 一个pattern文件,两个使用者:验证(模拟)、ATE(制造测试)

- 支持流行的Verilog simulators:VCS、NC-Verilog、Verilog-XL和MTI

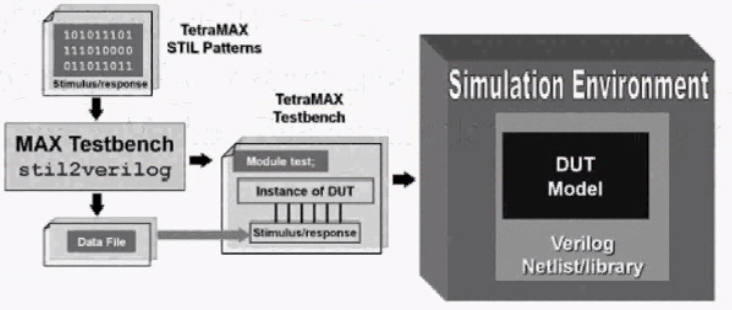

MAX Testbench flow

方法一——先生成STIL,再转换

从TetraMAX写出STIL pattern文件

使用STIL pattern作为输入运行stil2verilog以生成Verilog testbench

使用生成的测试pattern运行Verilog仿真

Example:

UNIX% stil2verilog <STIL_pattern_ file _name> <verilog_TB_file_name>

产生两个文件:

verilog testbench file: <verilog_TB_file_name>.v

Data file: <Verilog TB file name>.dat

方法二——在tmax中直接转换

在TetraMAX中将STIL pattern转换为Verilog testbench:

write_testbench -input <stil_filename>

-output <testbench_name>

[-replace]

[-config_file config_filename]

[-parameters { list_of _parameters} ]

Unified STIL flow

write_patterns -unified_stil_ flow(USF)

- 是单个STIL文件,提供所有可能的模拟模式(串行,并行,混合串行/并行和并行N移位),用于标准扫描和压缩扫描。

- USF可以与MAX Testbench或Verilog DPV一起使用

- STIL文件包含串行测试patern,并且是ATE的目标文件

- 消除了在并行负载下模拟压缩pattern的一些限制

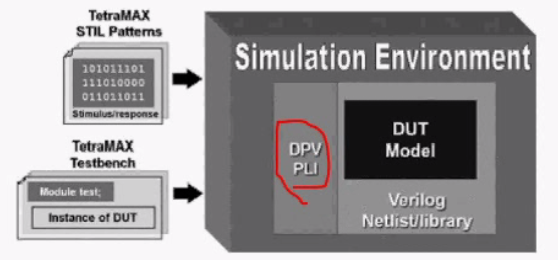

二、verilog DPV

使用PLl直接验证ATE-ready的STIL pattern

pattern可以“on-the-fly”模拟

支持流行的Verilog模拟器(PLI): VCS,NC-Verilog,Verilog-XL和MTI

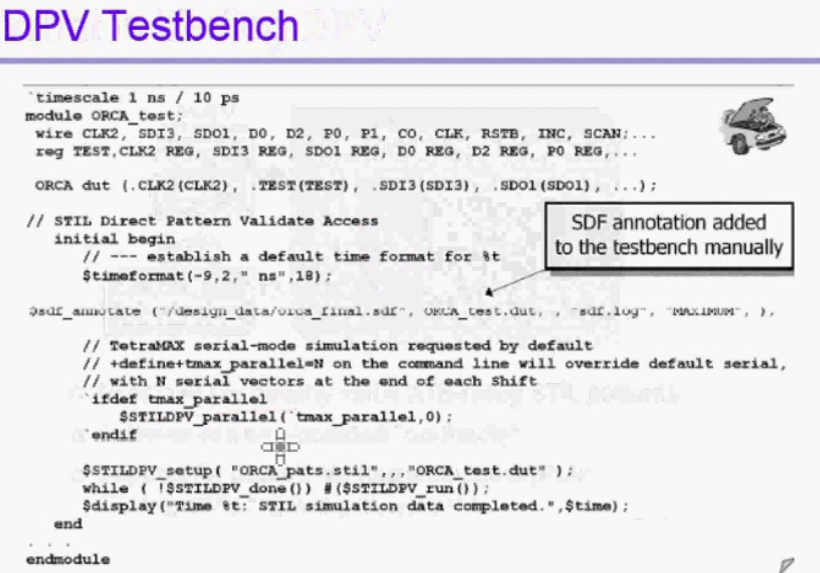

Simulate with Pattern

1. 写出不同类型的pattern

write_patterns all_pats.stil -format stil -parallel

write_patterns fast_pats.stil -format stil -parallel -type fast

- 对于每个类型的pattern,TetraMAX 产生 2个文件:

Testbench:all_pats_stildpv.v & fast _pats_stildpv.v

Patterns: all_pats.stil & fast _pats.stil

- Patterns来自all_pats_stildpv.v:$STILDPV_setup ( "all_pats.stil" ,,, "test.dut" ) ;

2.对all pats_stildpv.v仿真:

vcs -R -Mupdate +ace+2 +tetramax -P $STILDPV_HOME/lib/stildpv _vcs.tab +define+tmax_parallel=2 -v ./libs/io.v ./libs/core.v ./libs/bboxes_sim.v ./libs/rams_sim.v ./design_data/orca_final.v ./all_pats_stildpv.v $STILDPV_HOME/lib/libstildpv.a -l all_pats.log -o simv

3.在不更改testbench的情况下对Fast-Sequential patterns运行仿真:

unix% mv all_pats.stil all_pats.stil.bak

unix% ln -s fast_pats.stil all_pats.stil

unix% ./ simv -l fast.log

三、Debug ATPG模拟不匹配或ATE failure

-- 即使具有完美的STA和模拟的DUT模型而没有失配,实际的DUT仍然可能在ATE发生故障

-- 如果在STA和仿真中都使用了相同的ATE时序和post-route SDF,并且STA报告没有违规,则由于以下原因仍可能发生仿真不匹配:

-- 如果在STA和仿真中都使用了相同的ATE时序和路由后SDF,并且STA报告没有违规,则由于以下原因仍可能发生仿真不匹配:

- 仿真模式(zero,unit,typical)问题

- 基于0-delay环境预测的ATPG结果

- 仿真模型可能与ATPG模型不匹配

解决:

simulation失败了可以查看timing、设置等哪里出现问题;

如果已经到ATE阶段了,芯片流回来了,不能改了,但又不能让这些问题让整个设计block,因此使用命令将有问题的部分mask掉

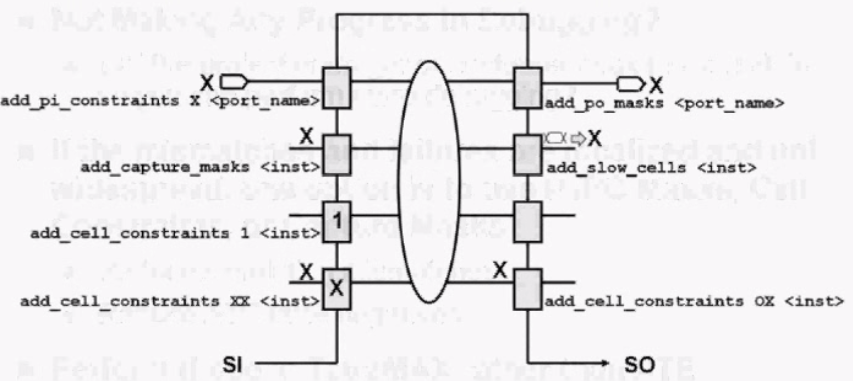

Masking Commands

定义output masks

输出掩码用于防止ATPG算法通过特定的输出端口观察故障,在屏蔽输出上不再观察到故障,因此覆盖范围将下降

add po_masks <port_name> l -all

Scan Cell Constraints

加载(0、1、X)到特定扫描单元中

add_cell_constraints < 0 | 1 | X > < chain | inst >

[ -position {< cell_ pos1 | sci > [cell_pos2] } | -all>>]

no-Scan Cell mask

add_capture_masks /PROBLEM/NONSCAN/FLOP

mask multi-cycle or false path

add_slow_cells <instance_path>

timing exception

set_simulation -timing_exceptions_for_stuck_at