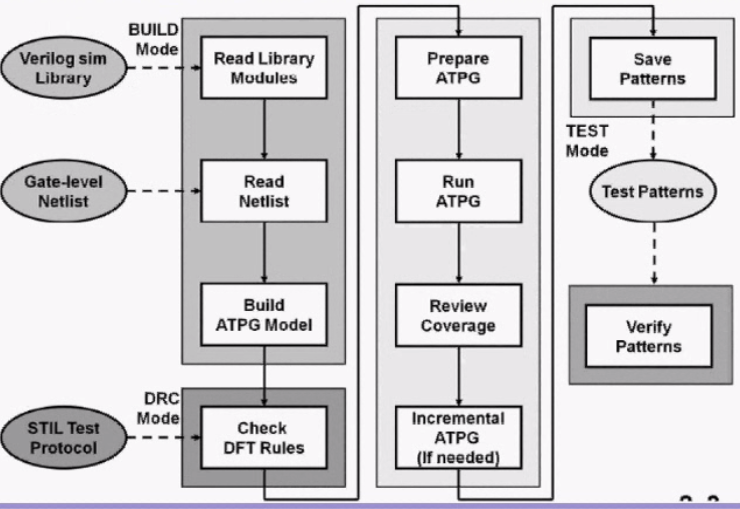

一、Build Mode

-

读入网表: BUILD-T> read_netlist /libs/0.18u/*/??DFF*.v (?代表1位,*代表n位)

- 若两个同名文件默认读入最后一个: set_netlist -redefined_module last | first

- 只能读structural Verilog libraries

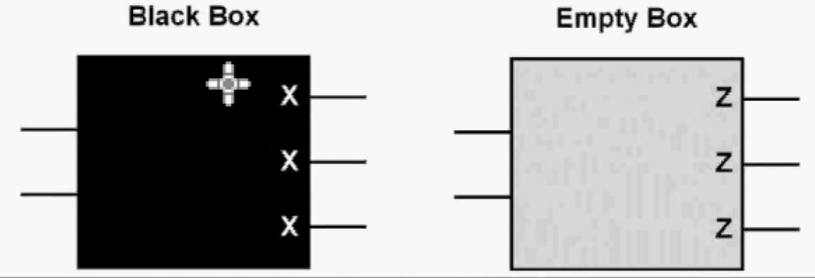

Empty Box VS. Black Box

set_build -reset_boxes; #Clears black & empty box list set_build -empty_box BUS SWITCH set_build -black_box RAM32x8 -empty_box IRQ_CORE # In Tcl mode, must use list for multiple black box modules: set_build -black_box [list RAM32x8 RAM64X8] # Report all black box modules: report_modules -black box

二、快速到达各个模式

(2)快速到达DRC Mode

第一次过程:

BUILD-T> read_netlist ...

BUILD-T> run_build_model

DRC> write_image pass1.image.gz -compress gzip -replace

随后的过程(快速到DRC mode):

BUILD-T> read_image pass1.image.gz

DRC-T>

(2)快速到达TEST mode

第一次过程:

BUILD-T> read_netlist . .

BUILD-T> run_build_model

DRC-T> run_drc DUT.spf

TEST-T> write_image pass1.image.gz -compress gzip -replace -violations

随后的过程(快速到test mode):

BUILD-T> read_image pass1.image.gz

TEST-T> #Ready to resume in TEST mode

三、Memory DFT

1.测试RAM / ROM内部fault

--无法通过门级stuck-at fault技术来测试RAM / ROM的晶体管级结构

--memory BIST(MBIST)通常用于测试内部memory fault

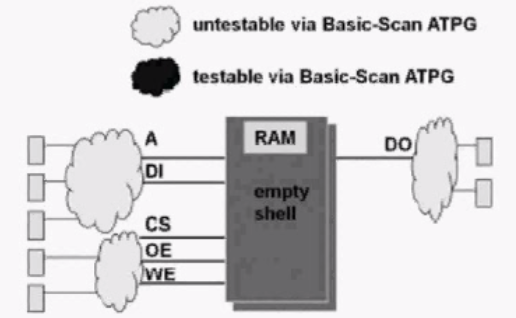

2.测试ATPG中的RAM / ROM 周围的逻辑

①应用black box模型(不推荐):

综合设计中的供应商RAM / ROM原语通常表现为black box,memory周边逻辑的覆盖率会很低

②对Basic-Scan ATPG使用bypass模式(常用):

如果memory支持bypass模式,则可以使用bypass模式来获取周围逻辑的覆盖范围

③编写顺序ATPG的功能模型(最好):

通过用用户提供的功能Verilog模型替换black box RAM / ROM单元,可以最大化周围逻辑的可测试性

(后两者可结合使用)

Black Box or Bypass Mode

非扫描顺序单元(包括memoty)会导致DFT阻塞

解决:

① 对RAM添加bypass,以便围绕RAM的某些逻辑可以使用Basic-Scan ATPG测试;

手动修复RTL(如果memory没有bypass模式);

② 使用TetraMAX model

-- 启用Fast-Sequential ATPG以允许TetraMAX通过memory进行测试

-- 将写入控制信号传递到top-level port:在顺序周期内控制写;在扫描移位期间保护memory

3.Memory应该clock稳定&load稳定

① momery is “clock stable”——如果当所有时钟都处于“off state”时其内容稳定

-- memory必须是时钟稳定才能被ATPG使用

② momery is “load stable”——如果momery在扫描移位期间处于稳定状态

-- 通常用有ScanEnable的memory的WriteEnable或ChipSelect信号来实现

-- 通过使用多个负载来测试memory周围的故障,从而使ATPG更加有效

-- 还具有降低scan shift期间功耗的好处

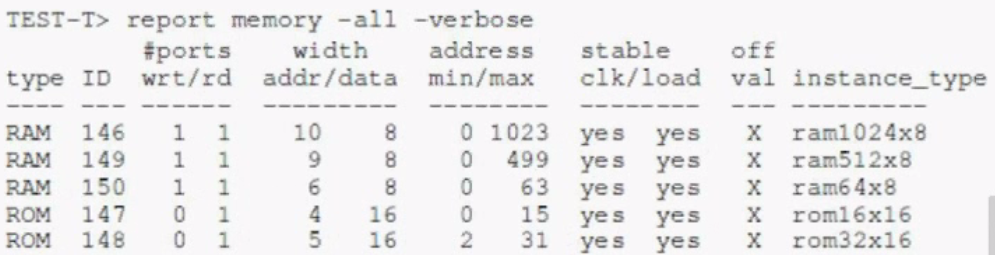

③ 报告memory的属性:

report memory -all -verbose

4.示例

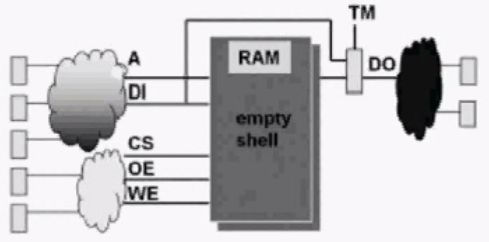

RAM model

本示例中的RAM具有level敏感的write和read端口

module MY_ATPG_RAM(read,write, data_in,data_out, read_addr , write_addr ); input read, write; input [7:0] data_in; //8bit data width input [3:0] read_addr; //16 words input [3:0] write_addr; //16 words output [7:0] data_out; //8 bit data width reg [7:0] data_out; //output holding reg reg [7:0] memory [0:15]; //memory storage event WRITE_OP; //event for write-thru always @(write or write_addr or data_in) if (write) begin memory[write_addr] = data_in; #0; ->WRITE_OP; end always (read or read_addr or WRITE_OP) if(read) data_out = memory[read_addr] ; endmodule

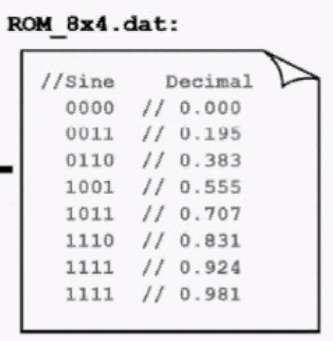

ROM model

module ROM_8x4 (ADDR, SINE); input [2:0] ADDR; output [ 3:0] SINE; reg [3:0] SINE; reg [3:0] ROM [0:7]; initial $readmcmb ("ROM_Bx4.dat” , ROM ); always @ ( ADDR ) if (ADDR<=7) SINE = ROM[ADDR] endmodule