PCIE是一种串行通信协议。在低速情况下,并行结构绝对是一种非常高效的传输方式,但是当传输速度非常高,并行传输的致命性缺点就出现了。因为时钟在高速的情况下,因为每一位在传输线路上不可能严格的一致,并行传输的一个字节中的每个位不会同时到达接受端就被放大了。而串行传输一位一位传输就不会出现这个问题。串行的优势就出现了,串行因为不存在并行的这些问题,就可以工作在非常高的频率下,用频率的提升掩盖它的劣势。

PCIE使用一对差分信号来传输一位信号,当D+比D-信号高时,传输的是逻辑1,反之为0,当相同时不工作。同时PCIE系统没有时钟线。

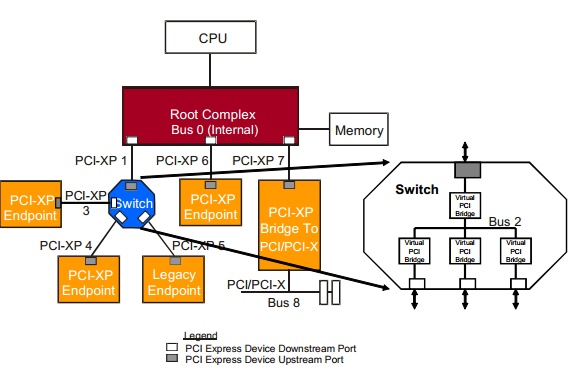

pcie总线的拓扑结构如图.1所示:

CPU连接到根聚合体(Root Complex),RC负责完成从CPU总线域到外设域的转换,并且实现各种总线的聚合,将一部分CPU地址映射到内存,一部分地址映射到相应的相应的设备终端(比如板卡)。

图.1 图.2

CPU读取一个PCIE设备的memory的过程如图.2所示

在PCIE的拓扑结构中,有一个非常重要的结构,它就是Root Complex(RC)结构。顾名思义,它负责将几个不同的总线协议聚合在一起,如内存的DDR总线,处理器的前端总线Front Side Bus(FSB)。在PCIE中,CPU的操作实际是由RC代替完成的,所以一定程度上也可以讲RC代表CPU。

所以当CPU想要访问Endpoint时:

Step1:CPU让RC产生一个MRd,经过Switch A,Switch B,到达Endpoint。

Step2: Endpoint 接受数据包,进行数据读取。

Step3:Endpoint返回一个带有数据的Completion.

Step4: RC接受数据包,给CPU。