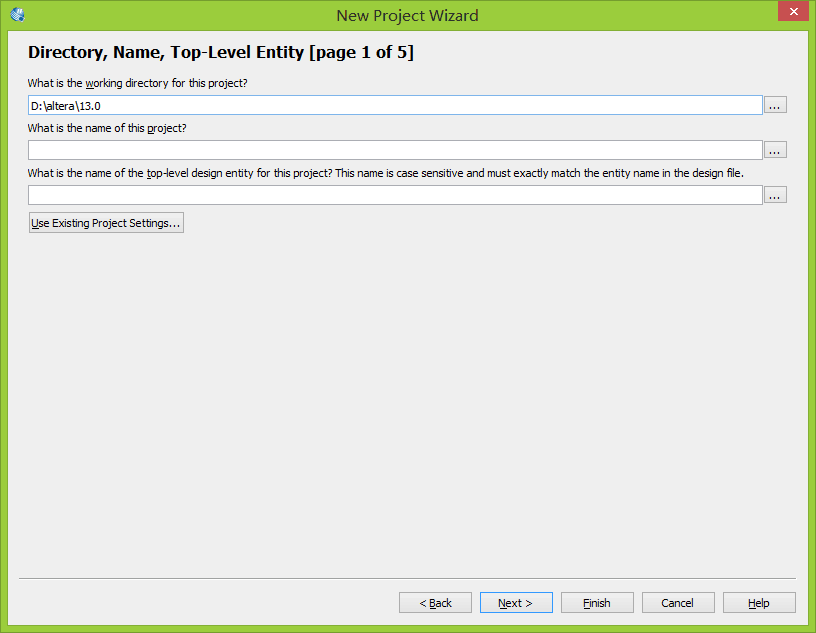

1、新建工程项目,填写项目存储路径和工程名,不要出现中文路径

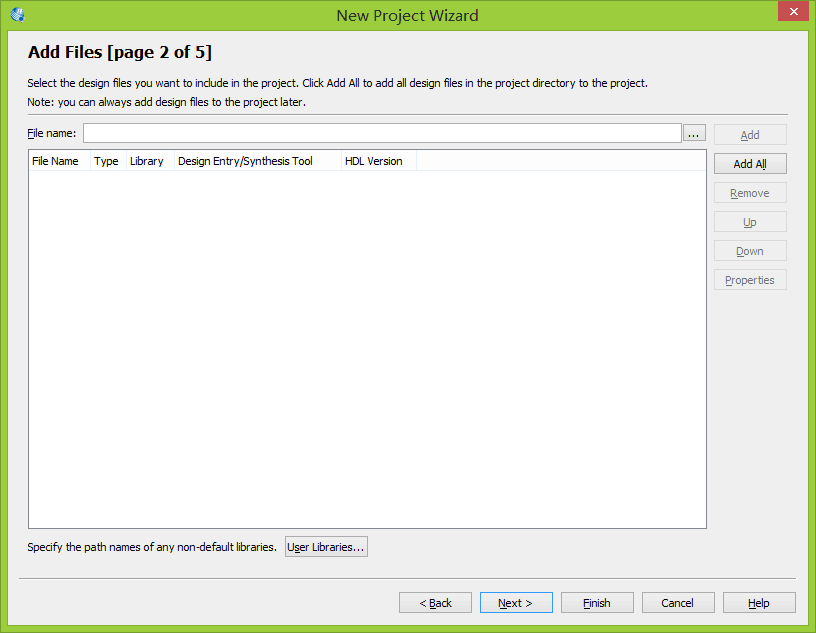

2、添加已存在文件(可选),在【File name】下选择已经存在的工程项目,利用【Add】或【Add all】命令添加文件到新工程,点击【Next】

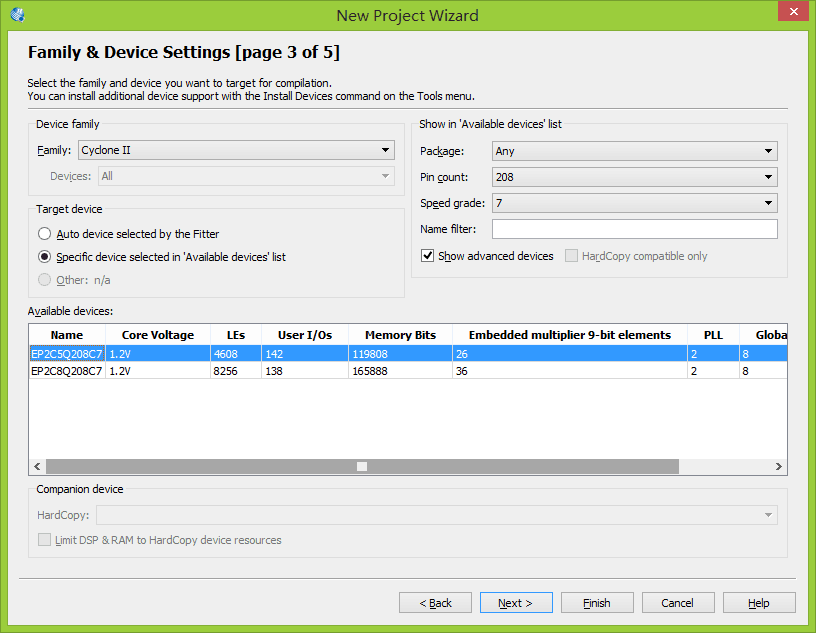

3、选择芯片类型,这里我选择ALtera公司的CycloneⅡ系列,208管脚,并在【devices】下选择具体芯片型号,点击【Next】

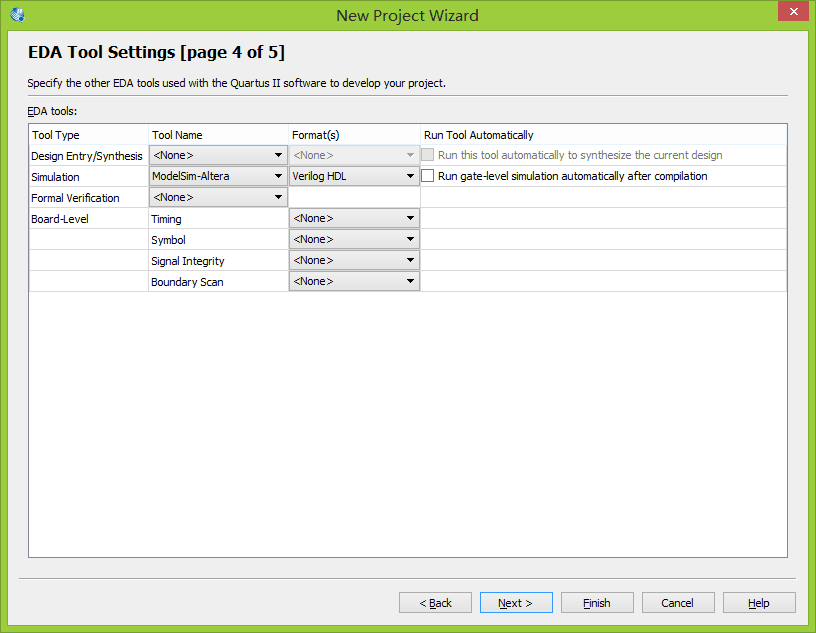

4、设置仿真器和描述语言,【Simulation】下选择仿真工具Modelsim,描述语言为Verilog HDL,点击【Next】

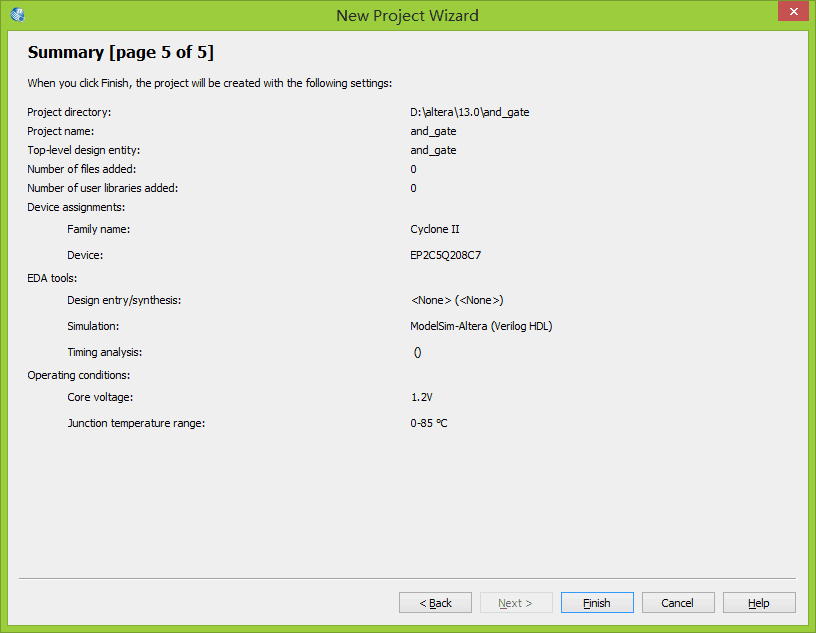

5、显示设置信息,显示了项目路径,项目名,顶层文件,芯片系列型号等设置信息,在检察符合需要后点击【Finish】。

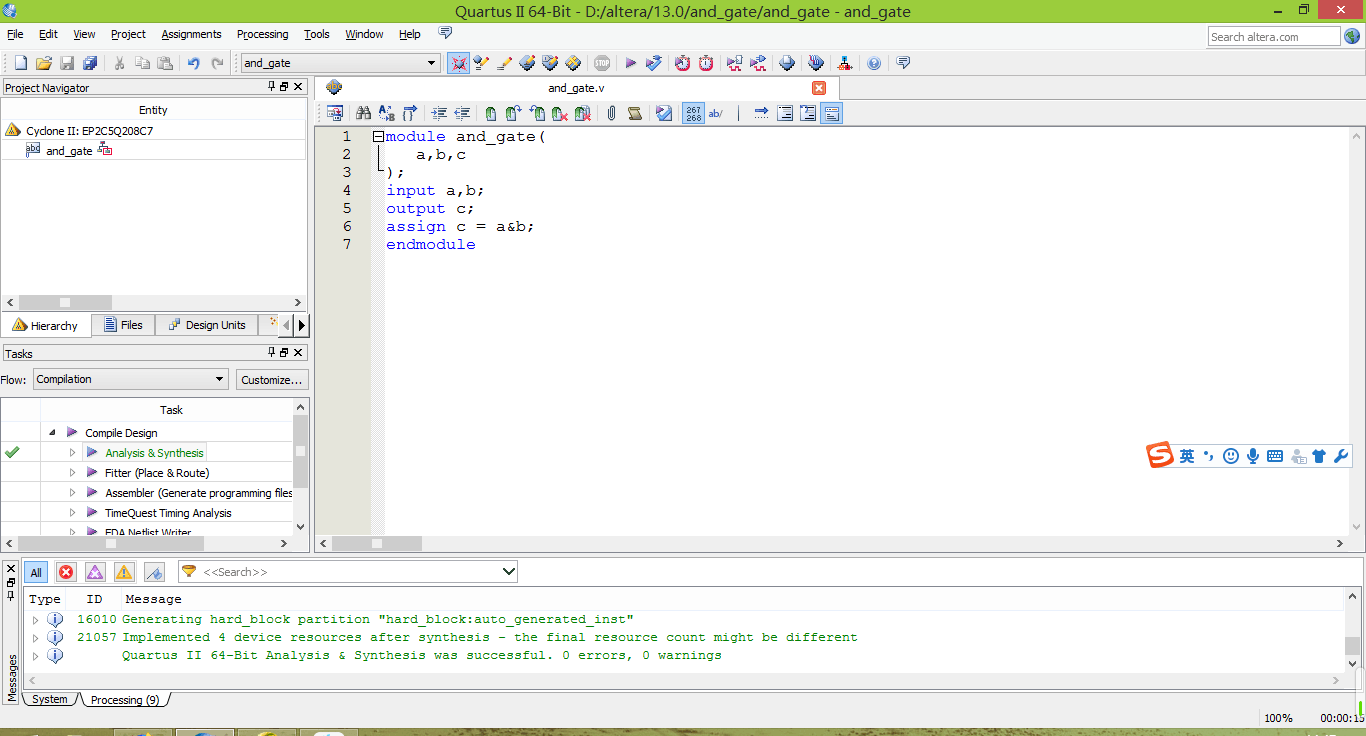

6、新建一个Verilog HDL File文件,这里写了一个简单的与门程序,命名最好与工程名一致

7、分析综合一下,确定无误后继续

8、创建test bench模板,Processing > Start > Start Test Bench Template Writer

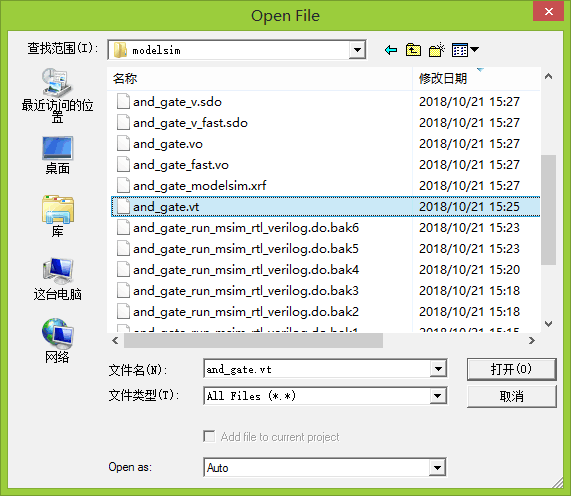

9、通过file >open >simulation >modelsim >找到.vt的文件打开(把文件类型改为全部文件),修改testbench加入激励信号(输入信号)

9、通过file >open >simulation >modelsim >找到.vt的文件打开(把文件类型改为全部文件),修改testbench加入激励信号(输入信号)

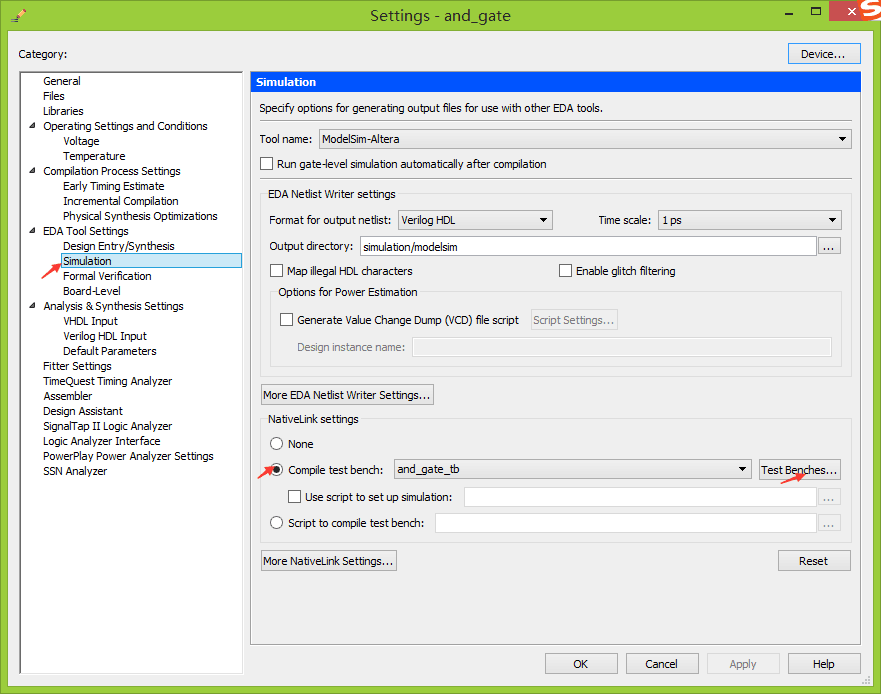

10、保存,编译,在仿真之前先要设置一下,Assignment > EDA Tool Settings ,点击Simulation,在NativeLink setting下,选择Compile test bench标签,单击Test Benches按钮

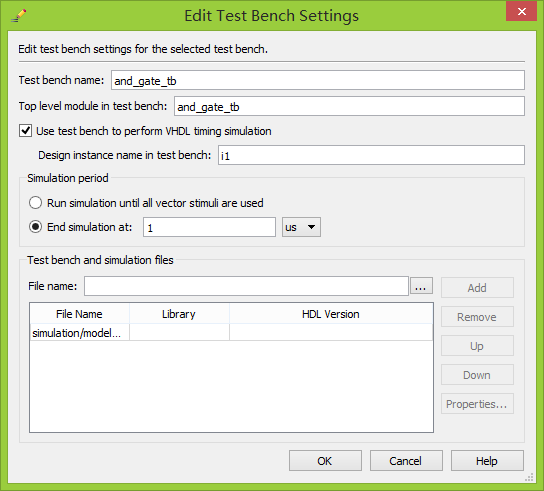

11、填写测试文件名。Test Bench Name 就是测试脚本的名字,在这里是and_gate_tb;Top Level Module in text bench 是在测试脚本中顶层模块的名字,在这里是and_gate_tb,Design instance name in text bench 就是在测试脚本中例化的名字,在本例中是:i1,设置仿真时间为1us,然后添加文件,点击三个ok退出

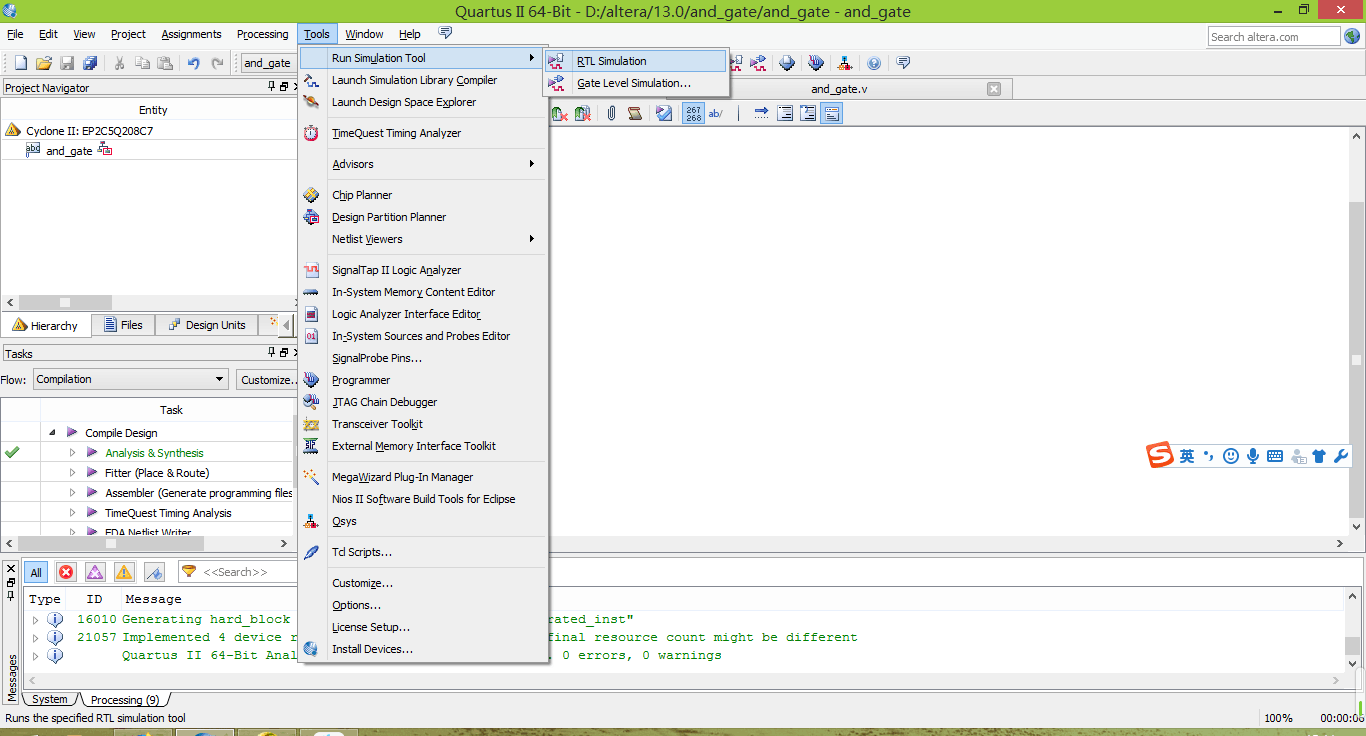

12、仿真,Tools -> Run EDA Simulation -> EDA RTL Simulatiom。

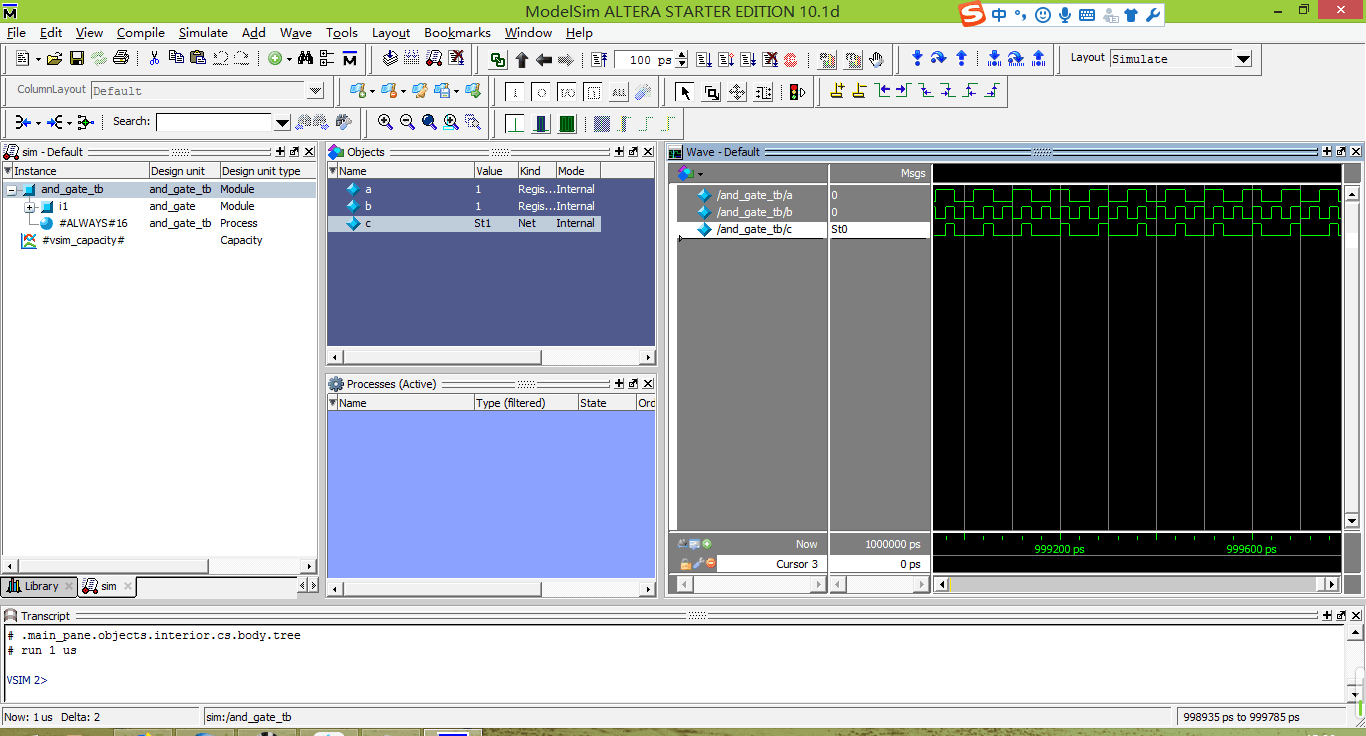

13、仿真结果如下:

13、仿真结果如下:

可以看到仿真波形符合与门的性质,只有当a和b同时为1时,输出信号c才为1。