always语句包括的所有行为语句构成了一个always语句块。该always语句块从仿真0时刻开始执行其中的行为语句;最后一条执行完成后,再开始执行其中的第一条语句,如此往复循环,直到整个仿真结束。因此,always语句块常用于对数字电路中一组反复执行的活动进行建模。比如大家熟知的时间信号发生,每半个时钟周期时钟信号翻转一次。

always @(posedge clock) begin ...... end

这就是条件循环语句了。

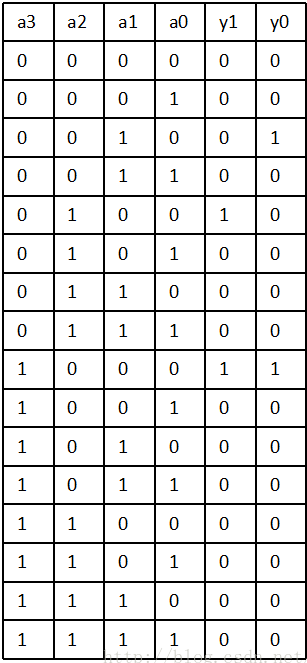

下面是今天做个一个小例子,4-2线编码器:

给出激励文件:

`timescale 100ns/1ns module testbench ; wire [1:0] y ; reg [3:0] a ; enc4to2 DUT ( .y (y ) , .a (a ) ); initial begin a[0]=0; a[1]=0; a[2]=0; a[3]=1; end always #2 begin a[0]=~a[0]; end always #4 begin a[1]=~a[1]; end always #6 begin a[2]=~a[2]; end always #8 begin a[3]=~a[3]; end endmodule