standard cell timing model 主要包括两方面的信息:

Cell Delay calculation

Output Transition calculation

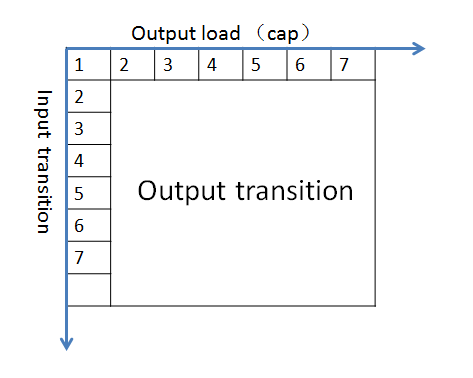

首先,cell delay 和 cell output transition这两者都是根据 input trans 和 output load 计算出来的;

具体应该是 input pin transition 和 output net total cap 来计算:

这里的 input transition 就是上一级cell 的output transition,而 cell output transition 的计算也是由 input trans 和 output load 决定的:

以此逐级类推计算,就可以计算出 timing path 上所有的 cell delay 值了。

********************************************************************************

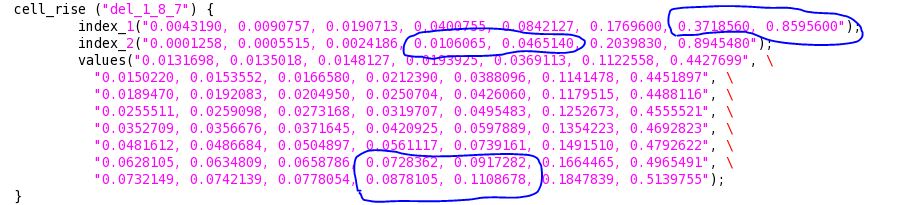

来看一个具体的 cell delay 计算实例:

上图中 SVN_BUF_10 这个 cell :

cell delay = 0.0861

input pin transition = 0.5727

output net total cap = 0.0182

基本原理是将input trans 和 output cap 这两个参数代入到 std cell 库中的 delay 计算表(lookup table),查出对应的 delay 值;

用 report_delay_calculation 可以报出计算过程:

图中的 Z 就是计算出来的 cell delay ,与 report 中的 0.0861 很接近;

具体计算过程是:

根据 X 和 Y 的值,在 lib lookup table 中查找到 X 和 Y 左右两侧的坐标点,将这四个坐标点代入二元拟合公式 Z= B*X + C*Y + D*X*Y ,就可以得到四个二元二次方程,由这四个方程可以解出 ABCD 四个系数的值,这样就得到了一个具体的拟合公式,然后再将 input trans 和output cap 代入拟合公式就可以计算出这个cell 的delay 值了。

******************************************************************************

lib lookup table 如下:

在 lookup table 中,

index_1 是 input trans,是纵坐标

index_2 是 output cap,是横坐标

有了横纵坐标,就很容易查出 delay value了

#################################################

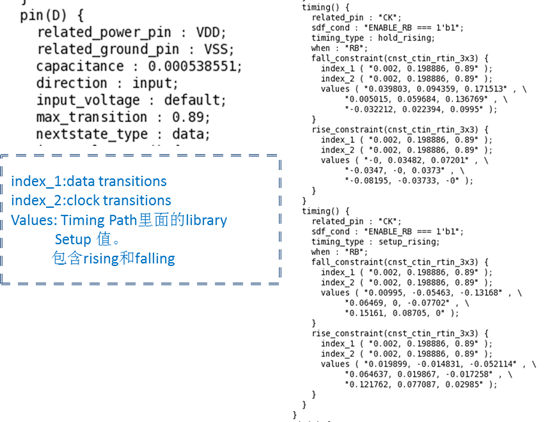

以上是 组合逻辑 cell delay 计算,那么 sequential cell 的 delay 如何计算? 比如 register ?

register 的 delay 包括两个: cell delay (即 CK -> Q 的delay), library setup time (即 CK 端的 setup window)

a)register cell delay 的计算:根据CK 端 input transition 和 Q 端 output cap,查表得出

b)register library setup time 的计算:根据 D 端data input transition(index_1) 和 CK 端 clock input transition(index_2), 查表得出

*********************************

| ^_^ | ^_^ |