使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用。本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA 的寄存器或者 RAM。

一、ZYNQ AXI 总线拓扑结构图

黄色部分即为 FPGA 部分。

二、新建 AXI_Lite 寄存器列表

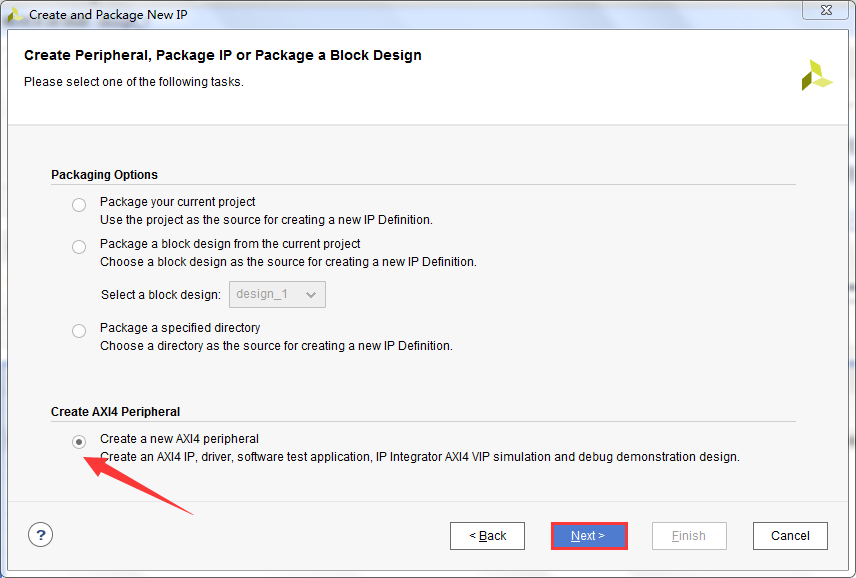

1..点击主页上方菜单 Tools --- Create adn psckage IP ,点击Next

2.选择第四项,Next

3.选择 IP 名称和存放的路径,Next

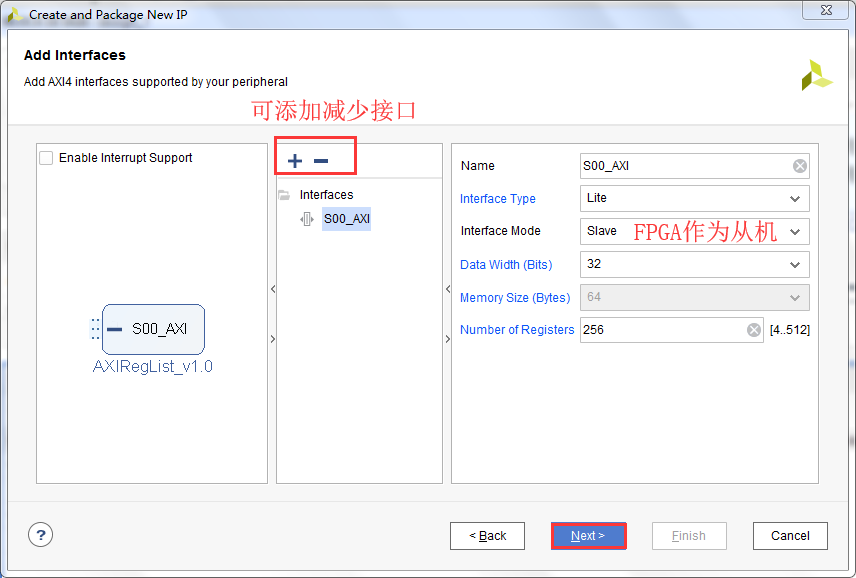

4.设置 256 个存储空间(每个存储空间默认位宽为32)

5.选择编辑 IP 看看生成的代码,也可以直接选择第一项。

6.Vivado 打开了一个新的界面,此界面和原界面略有不同,注意分别。

7.可以打开代码看看是什么,可以在里面加入用户逻辑代码。

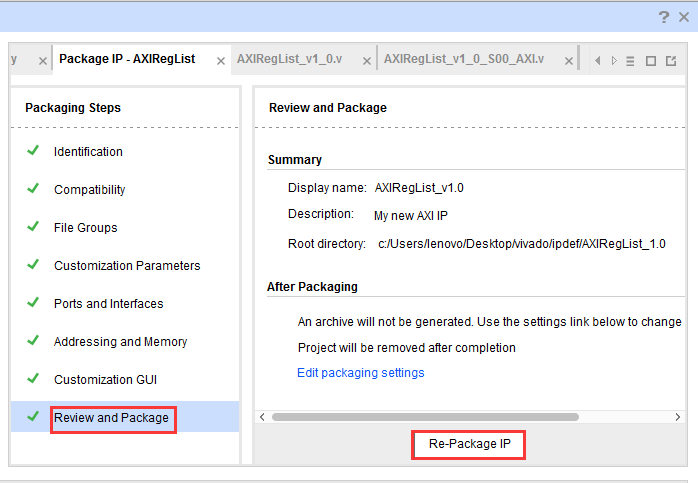

8.其实已经创建好了 IP,如果有改动则需要点击下面这项,之后此界面会自动关闭

9.选择 Settings --- IP --- Repository,可以看到这个 IP,也可以在这添加第三方 IP

三、调用IP

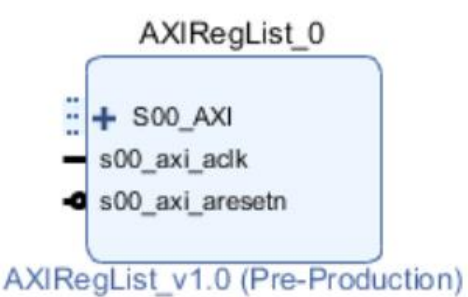

1.主界面打开 Create Block Design,点击 + 号,即可添加我们定义好的 IP,有3个口,从口,时钟,复位。

2.AXI IP有从口,因此ZYNQ得添加主口,打开 ZYNQ,添加时钟、复位、UART、DDR、中断等,最重要的还要添加 Master GP0 接口

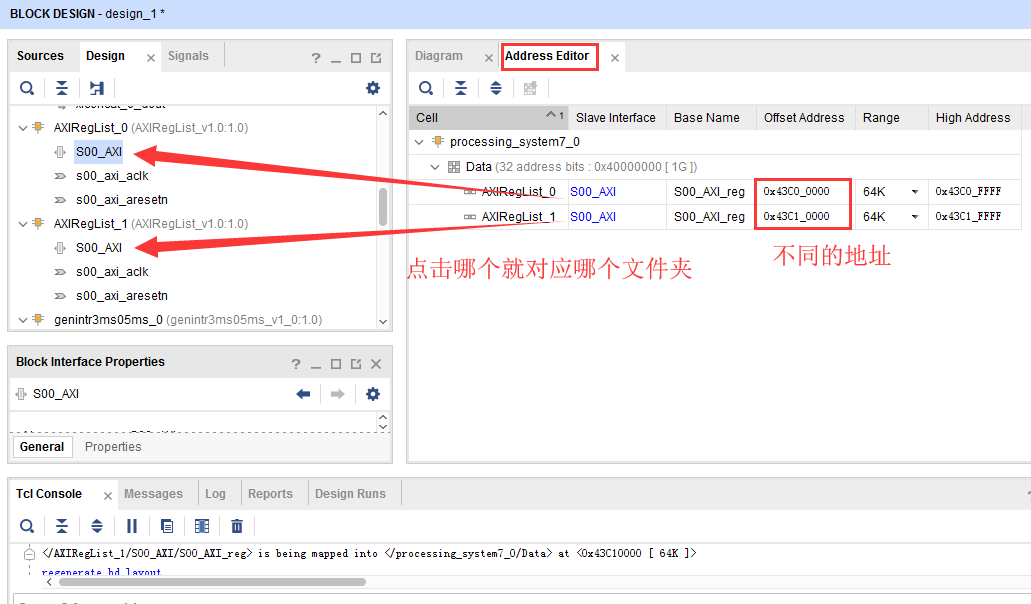

3.ZYNQ 的 AXI_ACLK 和 FCLK_CLK 手动连在一起,并且进行自动布线即可连好。(此处添加了2个一样的AXI IP)

4.在与视图仪器的选项卡中有个 Address Editor,可以看到系统自动分配的地址,当然用户也可以自定义地址

7.也可以添加一个 ILA IP 来观察 AXI 的波形,点击 + 号添加,按下图连线即可

6.之后就可以综合生成 bit 文件导出 HDF 文件进行软件设计。

四、普通自定义IP

见本人上篇博客《ZYNQ笔记(6):PL精准定时中断》。

五、常用 IP

1.Vector logic :逻辑IP,用于产生与、或、非、异或

2.Concat:总线合并IP,可以将多个单位宽信号合并成一个多位宽信号

参考资料:

[1]V3学院FPGA教程

[2]何宾, 张艳辉. Xilinx Zynq-7000嵌入式系统设计与实现[M]. 电子工业出版社, 2016.