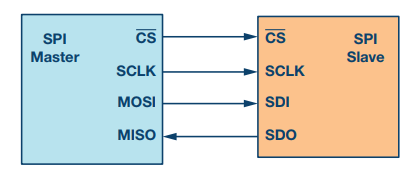

SPI(Serial Peripheral interface)是由摩托罗拉公司定义的一种串行外围设备接口,是一种高速、全双工、同步的通信总线,只需要四根信号线即可,节约引脚,同时有利于PCB的布局。正是出于这种简单易用的特性,现在越来越多的芯片集成了SPI通信协议,如FLASH、SD卡,AD转换器等。SPI的通信原理比较简单,它以主从方式工作,通常有一个主设备和一个或多个从设备。一般其有 4 根线,片选线(CS)、同步时钟线(SCLK)、输入数据线(MOSI)和输出数据线(MISO)。

一、通信模式

一般而言,SPI通信有4种不同的模式,不同的从设备在出厂时被厂家配置为其中一种模式,模式是不允许用户修改的。主设备和从设备必须在同一模式下进行通信,否则数据会接收错误。SPI的通信模式是由CPOL(时钟极性)和CPHA(时钟相位)来决定的,四种通信模式如下:

模式0:CPOL = 0, CPHA = 0; 模式1:CPOL = 0, CPHA = 1; 模式2:CPOL = 1, CPHA = 0; 模式3:CPOL = 1, CPHA = 1;

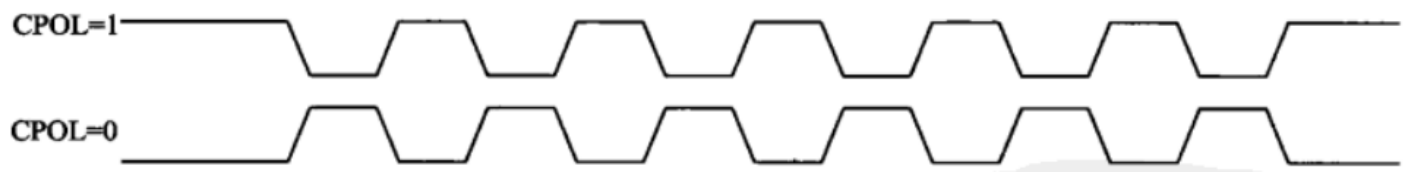

1.CPOL时钟极性

CPOL信号控制着SPI_CLK的时钟极性,时钟极性变化规律如下:

CPOL = 1:SPI_CLK空闲时为高,第1个时钟沿为下降沿 CPOL = 0:SPI_CLK空闲时为低,第1个时钟沿为上升沿

2.CPHA时钟相位

CPHA信号控制数据与时钟的对齐模式,其不同模式下的时序图如下所示:

由上图可知,当CPHA = 1时,时钟的第一个变化沿(上升沿或者下降沿)数据开始改变,那么也就意味着时钟的第2个变化沿(与第一个变化沿相反)锁存数据;当CPHA = 0时,数据在时钟的第一个变化沿之前就已经改变,并且保持稳定,也就意味着在时钟的第一个变化沿锁存数据。

二、总结

参考资料:

[1]亚德诺半导体.一文读懂4线SPI

[2]威三学院FPGA教程

[3]正点原子FPGA教程