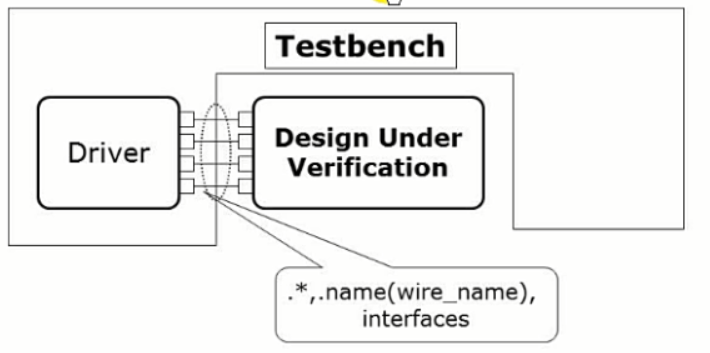

本节主要内容:testbench与design的连接,verilog连接testbench与design的方法,SV的interface,stimulus timing,clocking blocks,timing region,program block。(感觉很抽象)

一:design与testbench的连接

1:连接符号

.*

.name(wire_name) :verilog中使用方法

interface

2:verilog连接方式

3:sv连接方式

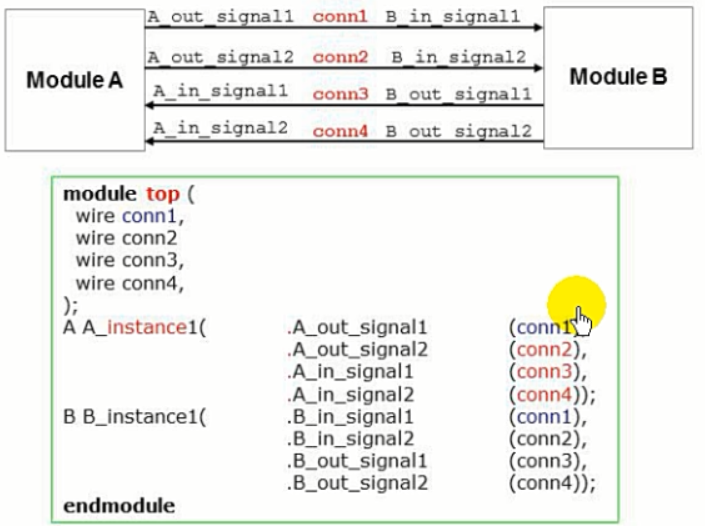

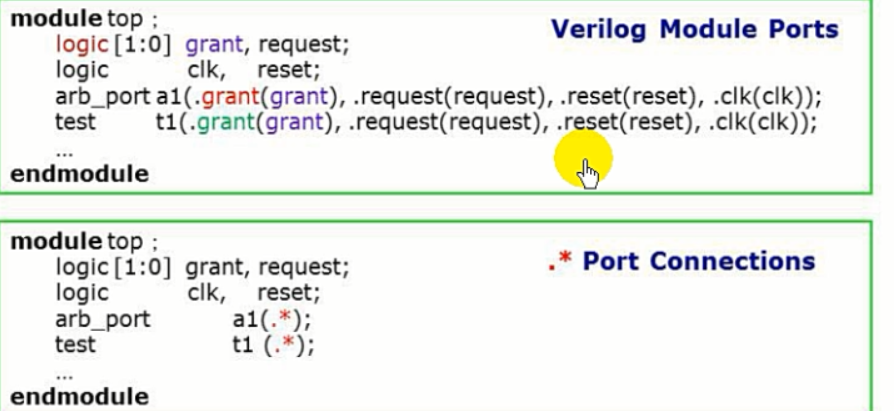

(1).* 通配符,对相同名字自动匹配

要求:有相同的名字,位宽相同

例如:

(2).name

相同名字与相同位宽,可以直接使用.name;括号内可省略

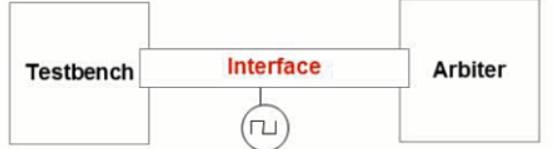

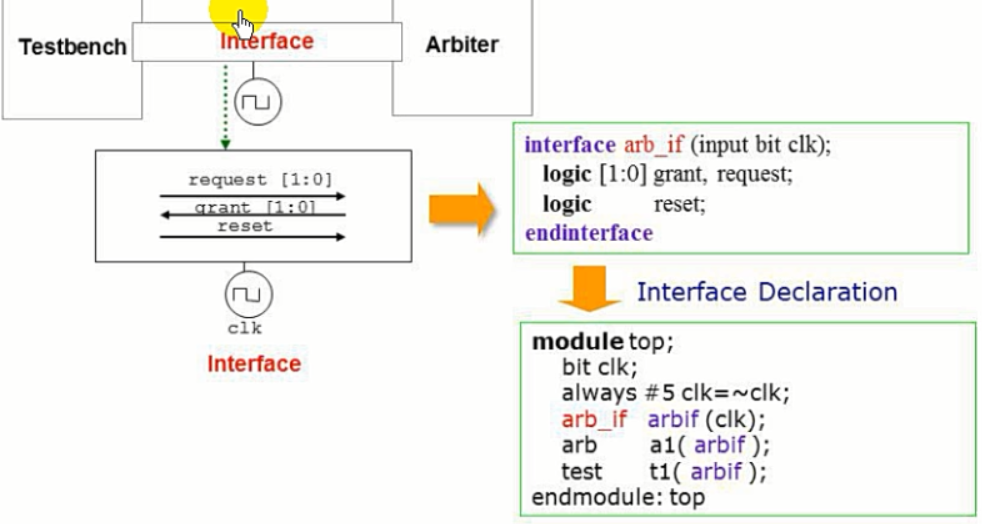

(3)interface

当名字不同时,上述方法不方便;而且若使用verilog方法,每个端口都要写,在复杂设计中很冗余;在sv里我们引入interface的概念

二:interface

1:定义

新的端口类型,将多种信号group一起,信息封装,重用。声明一次即可

2:使用

在interface里面声明信号,clk是外部输入的信号,内部信号为logic信号,为异步信号;

在top层内例化,如上图,现例化arbif这个interface,在使用该interface;

arbif.clk可访问里面的clk的信号;

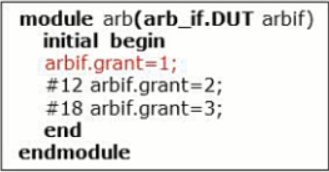

3:interface可用于设计

4:interface-modport

提供了另外一种interface信号,是modport的简写;一个interface里面可有多种modport的定义

例如:modport TEST (output request,reset,

input grant,clk );

设计中使用modport:module arb(arb_if.DUV arbif);

5:总结

可以包含function;不仅仅是线的集合;在系统集成上较方便;可加上协议检查;

不包含hierarchy结构(不能再interface里面声明一个module)

三:stimulus Timing & Clocking Blocks

在design与testbench之间易产生竞争冒险的情况,例如不满足Tsetup的要求;可以通过提前驱动信号,滞后采样信号(同步)来避免。

1:在interface里面建模,在适当时间驱动,采样信号;驱动信号不能太晚,采样信号不能太早;

testbench与design要分离开;

一般驱动在时钟沿前,采样在时钟沿后;

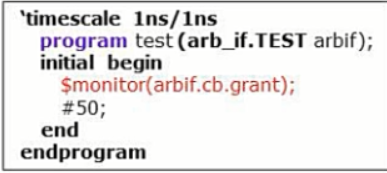

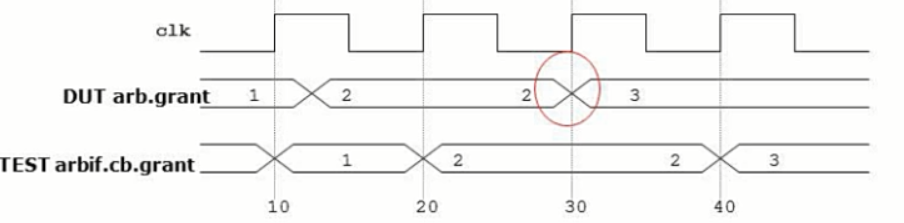

2:Clocking Block模块

为避免竞争冒险,interface里面使用clocking block模块;

**cb(clocking block简称以下)模块里的任何信号的驱动与采样都使用了同步的思想;

**cb模块只能用于验证,不能用于设计

**一个interface里面可包含多个cb模块

3:实现机理

使用cb,默认有 default input #1step output #0;(skew)

4:skew

input skew在时钟沿前有延时,output skew在时钟沿后有延迟

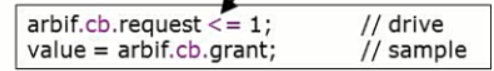

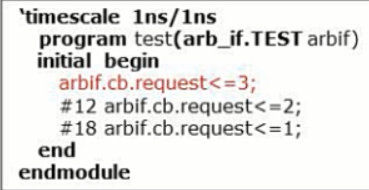

5:cb模块的使用(伪代码)

interface arb_if(input bit clk)

clocking cb @(posedge clk)

output request;

input grant;

endclocking //cb里面的信号都是同步信号

modport TEST(clocking cb,output reset) //表示使用cb里面的同步信号

endinterface

//使用cb信号

arb_if arbif;//声明一个interface

arbit.cb.request <= 2'b01; //驱动一个信号使用非阻塞赋值;采样一个信号用阻塞赋值

6:同步到信号

@arbif.cb.grant; @(posedge arbif.cb.grant); ##2 arbif.cb.request <= 0(等待2个时钟周期);

7:驱动信号非阻塞,采样信号阻塞

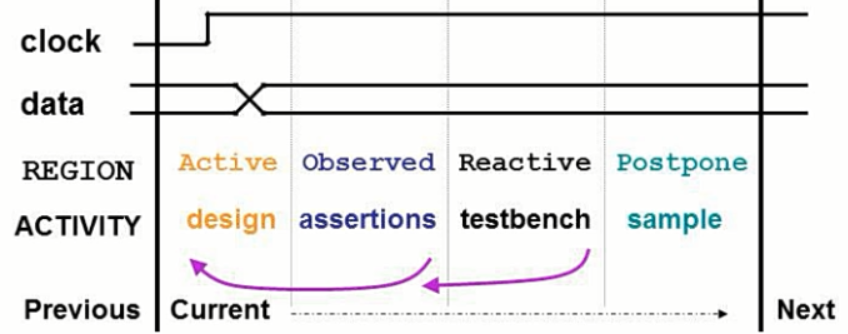

四:Timing Region

1:包含

active region:design区,design区可分为四个区(RTL的四个Time Region)

observed region:assertion区

reactive region:testbench区

postpone:sample区,采样所有设计的信号

2:interface采样区是在postpone,在时钟沿后采样时钟前的数据

波形如下图:

3:interface驱动,在时钟沿前驱动,时钟沿后得到信号的值

输出波形,这也就是非阻塞赋值的原因

五:program block

将OOP与DUT通过interface连接起来;在program里面可以跑设计。

1:类似于module,可包含代码,变量等;

没有hierarchy结构

2:例子

3:总结

不能有module hierarchy,可以有class hierarchy;

代码在initial块中执行,不能在always块;

在reactive区执行

六:一个完整的testbench模板

顶层设计:

子模块:

说明:

top层在active区执行,program在reactive区执行,这样可以避免race。