一: 所需文件

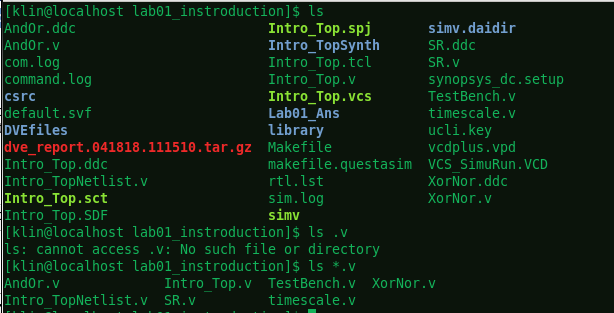

我们把v文件,makefile文件(vcs),tcl文件(dc)等放在工程文件夹里

1 :源文件 用ls *.v查看

顶层文件为Intro_Top.v。

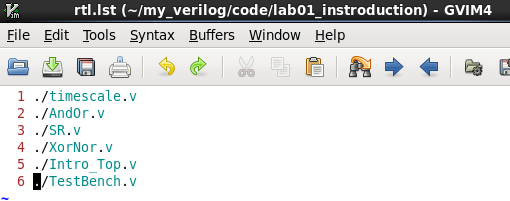

2:rtl.lst也放置了各个源文件的名称。有个问题,编译器怎么知道哪个是顶层文件,哪个是底层文件,文件之间的层次关系如何得到?makefile文件里也没说啊?

是根据rtl代码里的instance语句得到。

3:Testbench.v

initial语句不可综合

没有输入输出端口

4:makefile

makefile里面包含了仿真步骤;makefile.questasim是Questasim的仿真步骤文件。直接make运行的是makefile文件,make -f makefile.questasim运行的是makefile.questasim文件。

二:步骤

1:make 仿真

进行仿真,生成simv文件。如上节最后,make后可打开gui界面看波形,make.questasim直接打开gui界面;也可使用专门的波形软件verdi打开。

生成simv可执行文件,dcp波形(vpd文件),仿真中间文件放在csrc里。

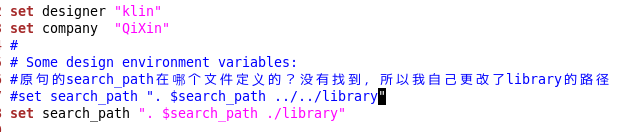

2:使用DC进行综合,dc_shell -f Intro_Top.tcl

脚本文件里的部分内容**注意search_path路径的设置。工艺库文件也放在项目文件中

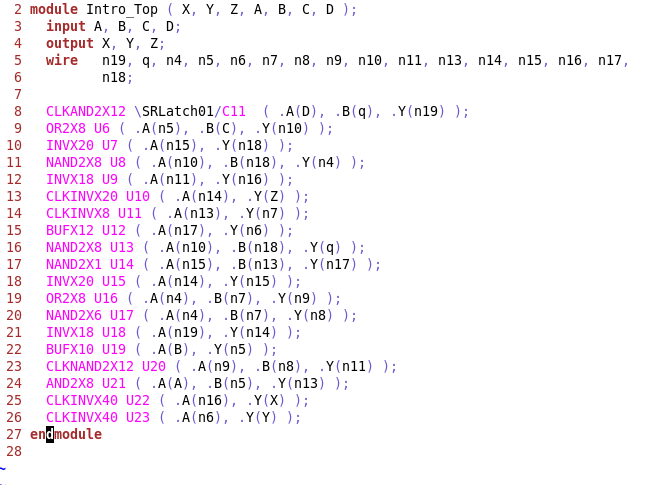

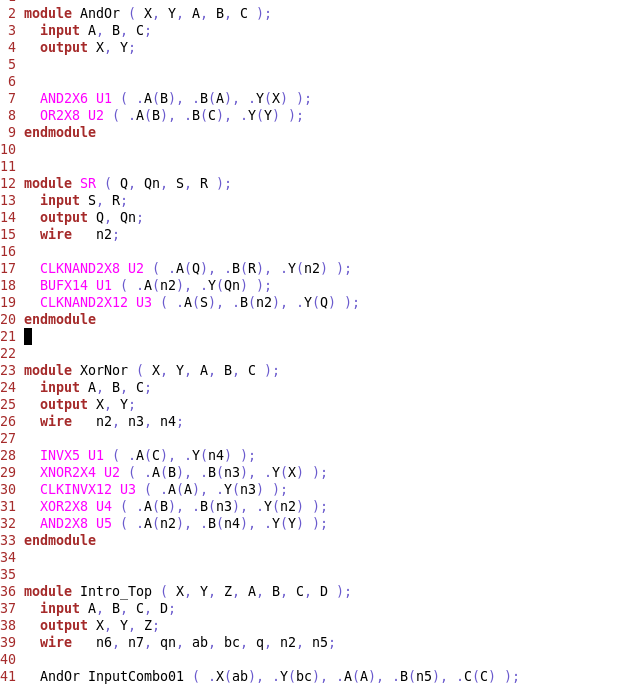

生成的网表文件如下图

添加ungroup -all -flatten,生成网表文件如下图,可见只有一个module,全部打散开来。