一:如何执行(编译执行)

1:编译链接生成二进制可执行文件

$vcs source_file[compile_time_options], 例如 vcs +v2k filename.v -debug_all (+2k指2001版本)

compile_time_options 可选项

A:基本可选项

-Mupdate :增量编译,再次编译时只编译改变的文件,提高速率

-R :run after compilation,编译后继续执行run

-gui :打开DVE图形界面

-l<filename>:set log file name,用于写编译信息,大型项目中经常使用,如 -l compile.log

-sverilog :支持system verilog

+v2k :支持verilog2001的标准

B:工艺库可选项

-v lib_file :lib_file(工艺库名字) RTL代码里涉及到工艺库

-y lib_dir :告诉vcs到哪里找这个工艺库

+libext+lib_ext:当用到很多库,代替-v

+incdir+inc_dir:代码里如果有include,使用这个命令告诉vcs包含文件的位置。verilog代码里面写`include "filename.vh"

C: 文件可选项

-f file :当有很多源代码时,将这些源代码整合到file里

D:修改可执行文件名字

-o foo :可执行文件名为simv,使用此命令改名字; 如 -o my_simv

F:define 一个宏

+define +<macro_name>=<value> :macro_name 宏名;value 初始化值; 如+define+INCR_COUNTER

2:执行

$simv[run_tiime_options]

例如 ./sim -gui &(./指在当前文件,sim指编译得到的可执行文件,gui指打开vcs的gui界面-dve,&指后台执行)将会得到执行的PID值

-s 结束仿真时间

$plusargs() 动态接收参数

-E echo

-l logfile 把仿真信息写入logfile文件里

二:基本知识

1: verilog compiled simulator;包含PLI 1.0/VPI接口(调用c++/c的程序);

2: 支持多抽象层仿真

行为级描述(验证,不可综合) - RTL级描述(设计,寄存器传输级) - Gate-level(门级,RTL级经过综合得到,与具体工艺 库相关,TSMC,SMIC,CSMC)

三:vcs debug

三种debug方法:system task calls,VCS UCLI,VCS DVE(GUI)

考虑因素:速度,信号可见性,信号。。可用性

1: system task calls

$display 打印变量赋值前值

$montor 打印变量赋值后值,变量值改变,打印值也变

$time 仿真时间

$readmemb 将文件里的内容读入存储器中,读二进制binary

$readmemh 将文件里的内容读入存储器中,读十六进制hexadmecimal

2: VCS UCLI命令行 效果不好 $vcs filename +v2k -ucli -R

3: DVE

根据此笔记的一打开DVE软件,DVE支持交互式仿真(在终端输入命令),支持后仿分析

tips1:task里面的参数在波形上显示不出来,所以最好使用display显示出来

tips2:debug

f10 单步执行(括号加外箭头),f11单步且进入函数体执行(括号加内箭头);每次单步仿真结束需点下箭头重新仿真方可再次仿真

tips3:波形知识点

F键:波形自动,全屏

group:将多个信号组成一组

set radix:波形的不同显示形式,十进制,二进制....状态机显示状态为set radix - state name

找波形里面具体数字有没有出现:右上角空-value-数字-前后点,可发现有没有这个数字

compare:选中比较的两个图形-signal-compare-name输入-creat-close

构造bus:选中信号-set bus-观察bus后的总线波形

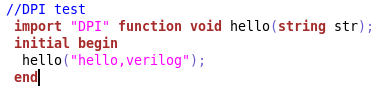

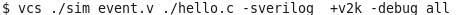

tips4:DPI (在verilog里调用c语言的代码)

第一步:写一个c文件,c文件要求:#include“svdpi.h“

第二步:在verilog源文件里添加调用c代码的语句

第三步:在终端执行编译命令时,添加c代码文件以及sverilog命令

第四步:终端执行 ./simv

显示hello,verilog

三:post-processing with VCD+ files

VCD(verilog change dump)是VCS的早期波形文件,VCD+是VCD压缩文件;大的项目波形文件很占内存与影响速度,所以产生了VCD波形文件,记录寄存器的值,层次等;将一些系统函数(例如$vcdpluson)嵌入到源代码中,编译仿真产生VCD文件(后缀名为vdp),打开DVE,参考log文档与波形文件,快速解决bug。

1:什么时候使用VCD+

当debug一个成熟的设计时,当仿真分析需要多名设计人员参与时,当仿真采用script(如makefile)时

2:VCD+的系统函数

$vcdpluson(level_number,module_instance)从module这个模块开始,记录number-1层

level_number: 0-记录特定模块的所有层次模块

1-记录特定模块的顶层模块

n-记录特定模块向内的n个模块

module_instance:以此模块为基准

$vcdplusoff(module_instance) 关闭

3:VCD+的编译执行

compiling: vcs files vcdplus_switches other_switches

files: sources files

vcdplus_switches: 更改vcd文件名,否则在simulator后默认生成vcdplus.vpd文件。+vpdfile

+vdpfilename.vpd

other wsitches: vcs的其他开关选项;

还有debug选项开关选项:-debug,-debug_all, debug_pp

simulate: ./simv

打开DVE,打开vcd文件:dve -vpd vcdplus.vpd。 或者dve &—>file—>open database—>vcdplus.vpd

4:在源代码如何添加系统函数

`ifdef dumpme

$vcdpluson();

`endif

通过是否定义dumpme(一般在脚本的complier里定义宏)+define+dumpme

5:$test$plusargs 键盘动态接收参数

6 : 在已有makefile文件的基础上,使用VCD文件的步骤

make clean -> make com -> make sim -> dve &(或者dve -dvp vcdplus.vpd) -> 查看波形,可双击波形上的某个数值进入源代码 - >debug

7:readmemb:将文件里的内容存在数组里。一般在VCD文件里没有数组的波形,可使用$vcdplusmemon将数组导入。

8:$display

$display("hello verilog ",`__FILE__,`__LINE__); //打出具体文件具体行的hello verilog,两个下划线

![]() //打出的hello,verilog为红色字体

//打出的hello,verilog为红色字体