- 本文为物理综合面试系列(16篇)的最后一篇文章,皆在给学员提供一个检验自己物理综合水平的平台和环境.

- 本文针对设计中常见的时序现象,精心设计了电路.意在通过电路的实现,体现给大家正确的设计方法和ASIC流程

- 本电路充分考虑到了国内目前的ASIC水平,难度偏难,请大家根据自己的目标合理选择方法和策略

- 本电路的代码及实现方法,满足从RTL到GDS2的设计需求

- 本电路的物理实现,涉及DC,DFT,MBIST,EDT,PT,ICC等相关内容,可以视为成熟设计的具体物理实现

- 欢迎大家积极参与,并对本案例的实现提供宝贵的建议

- 希望对大家的面试和工作有帮助

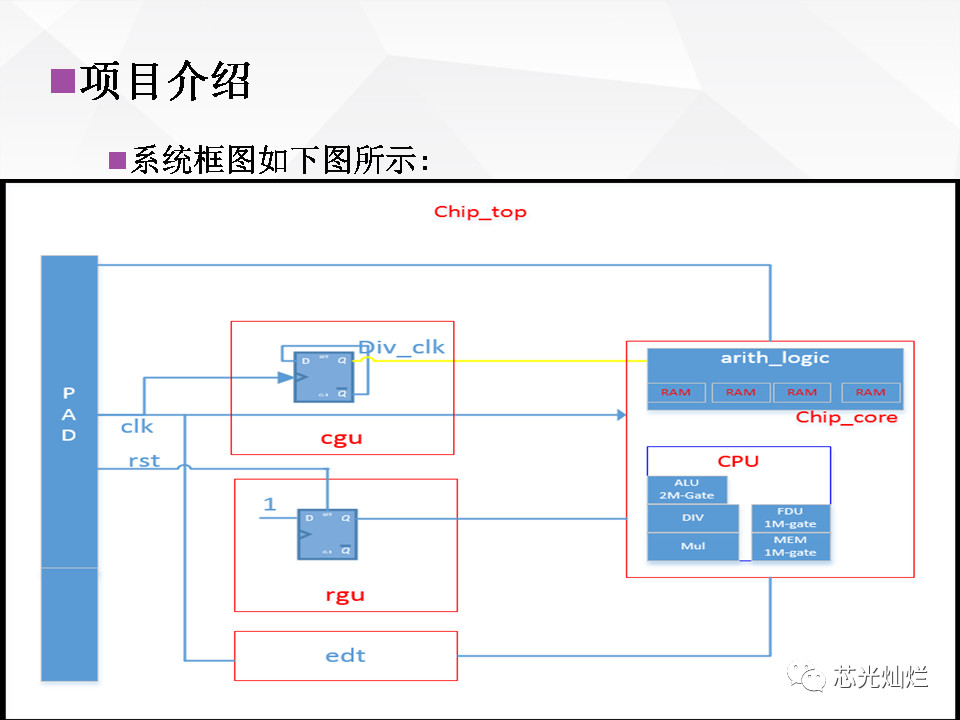

项目介绍

- 采用国内主流工艺:0.18um

- Clk要求功能模式满足180MhHz(取决于DC策略及ICC实现方法,做的频率越高越好)

- DIV/MUL相关部分指令,满足2 cycles要求

- Edt_channels=8

- 64 scan chains

- 具备DFT能力(满足扫描链插入,EDT压缩,存在MBIST电路)

- 满足DFT设计中DFV相关部分要求(针对DFT学员,要求提供相关DFT报告)

- 针对APR,要求合理配置电源系统,满足功耗优化和IR-DROP在合理范围(针对APR部分,请添加xgcl_wei私聊索取物理数据)

更多资讯,请关注个人公众号:芯光灿烂