在使用Verilog进行数字设计或者构建验证平台时,如果连接模块端口的线网或变量的宽度与端口定义的宽度不一致,在进行仿真时将有可能出现逻辑功能与期望不一致的情况,本文将对此类情况进行示例分析。

首先,在IEEE 1364-2001中,模块的端口对于信号的传输类似于连续赋值语句对于信号的传递,因此,对于连续赋值语句的要求也适用于信号通过端口的传递过程(对此可以理解,在具体物理实现后的是不存在模块端口的,信号将通过线网在电路中传输)。其次,Verilog中,与输入端口(input)和双向端口(inout)连接的数据类型只能是线网类型,和输出端口连接的可以是线网类型也可以是变量类型(具体连接的是线网还是变量取决于具体设计意图)。因为线网类型在传输过程中对于未声明线网处理的特点(参考前几期topic),那么在端口连接的过程中,可能存在端口宽度不匹配导致的部分线网未连接等情况的出现,而这些情况有可能导致逻辑功能异常。针对端口连接过程的特点,这里有以下几种情况可以需要分析:

1>端口宽度和连接线网或者变量的宽度一致;

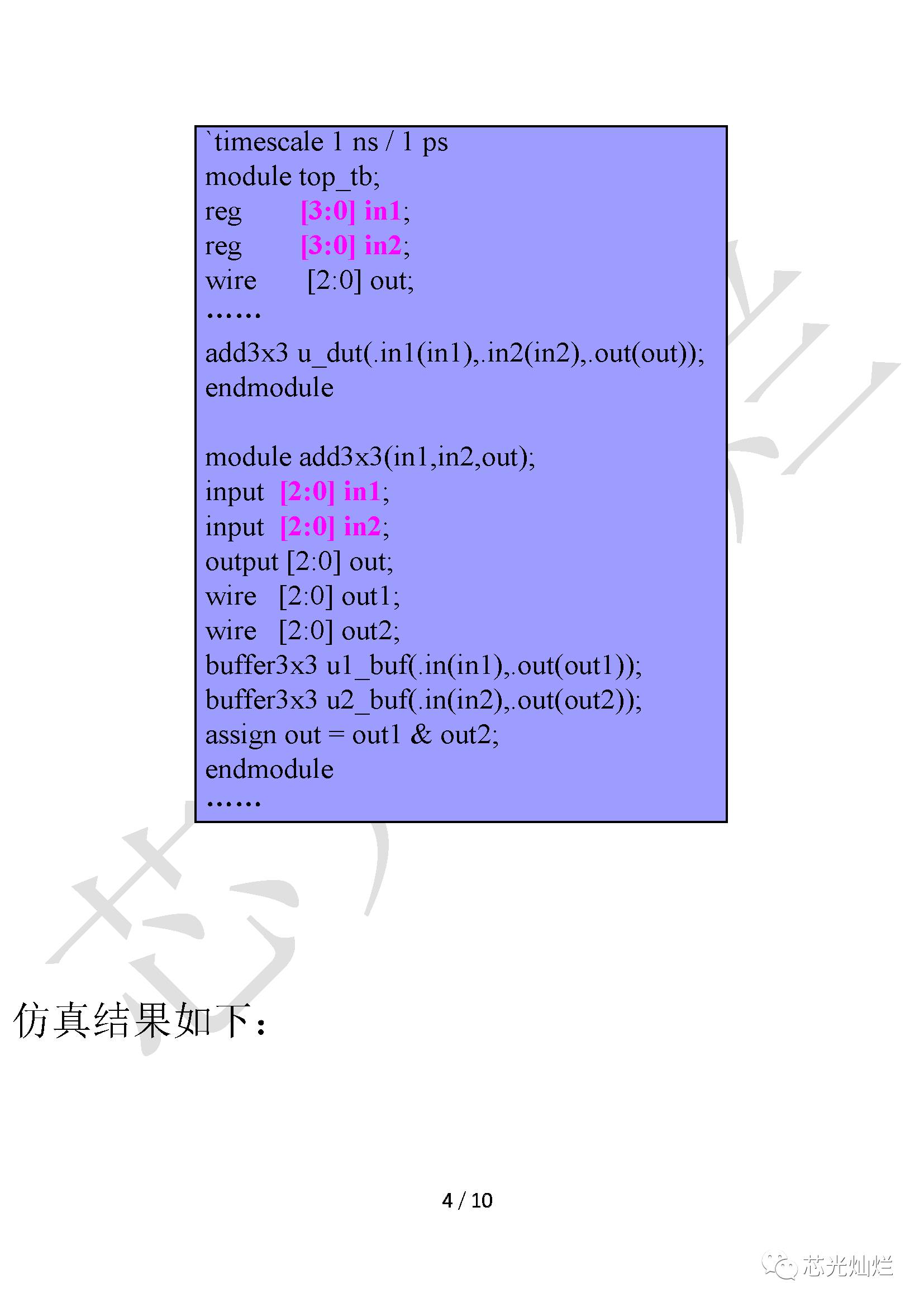

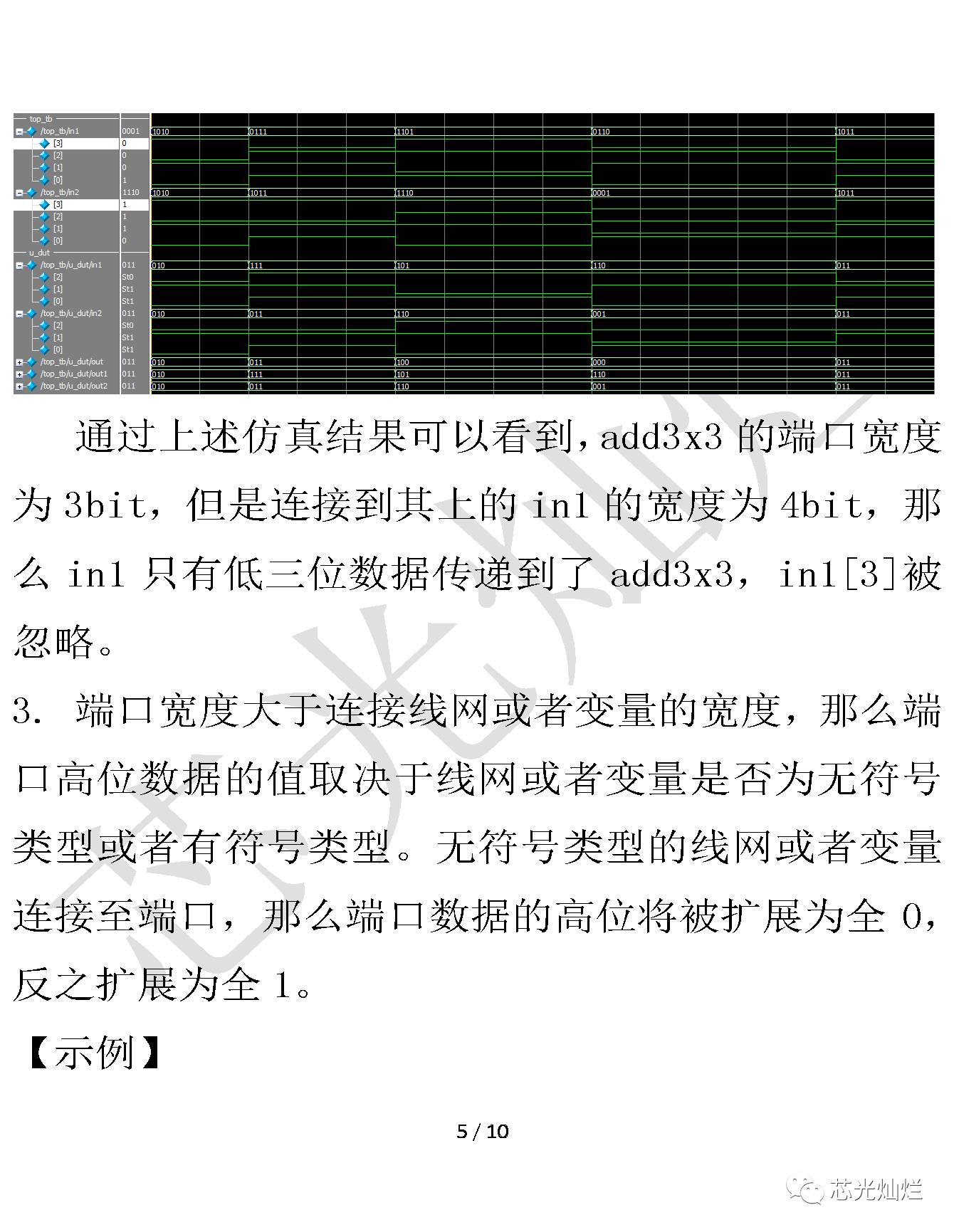

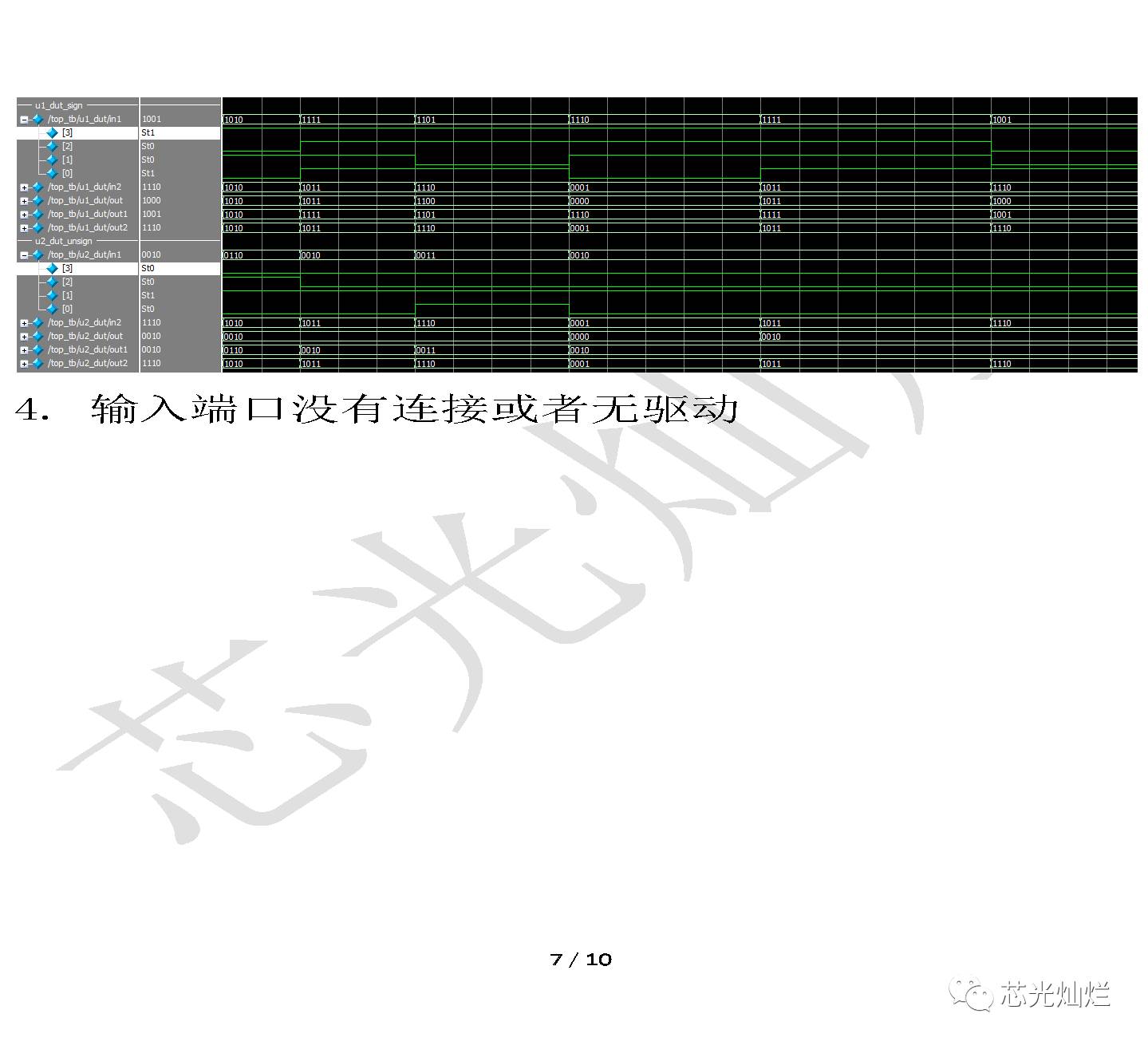

2>端口宽度小于连接线网或者变量的宽度;

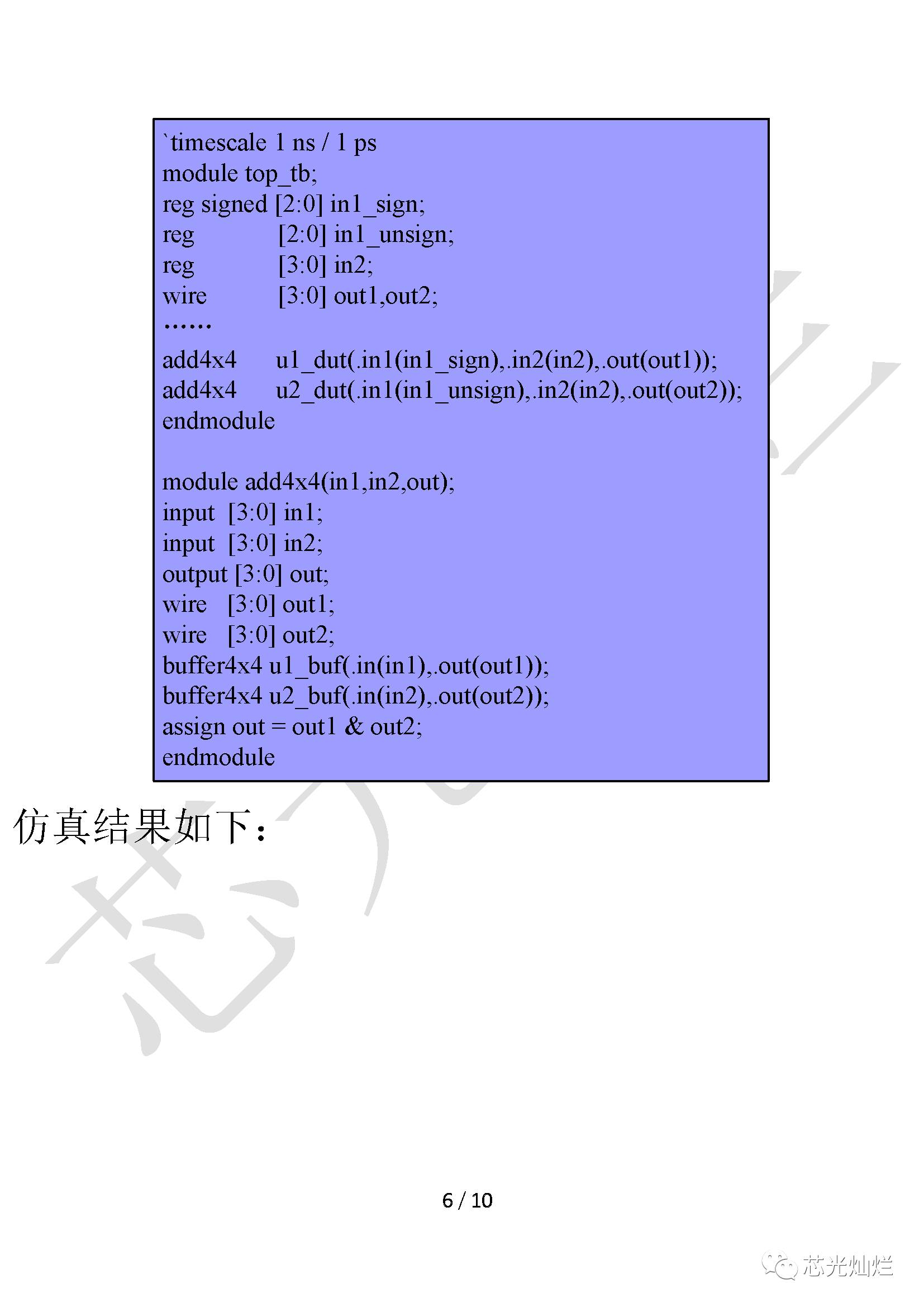

3>端口宽度大于连接线网或者变量的宽度;

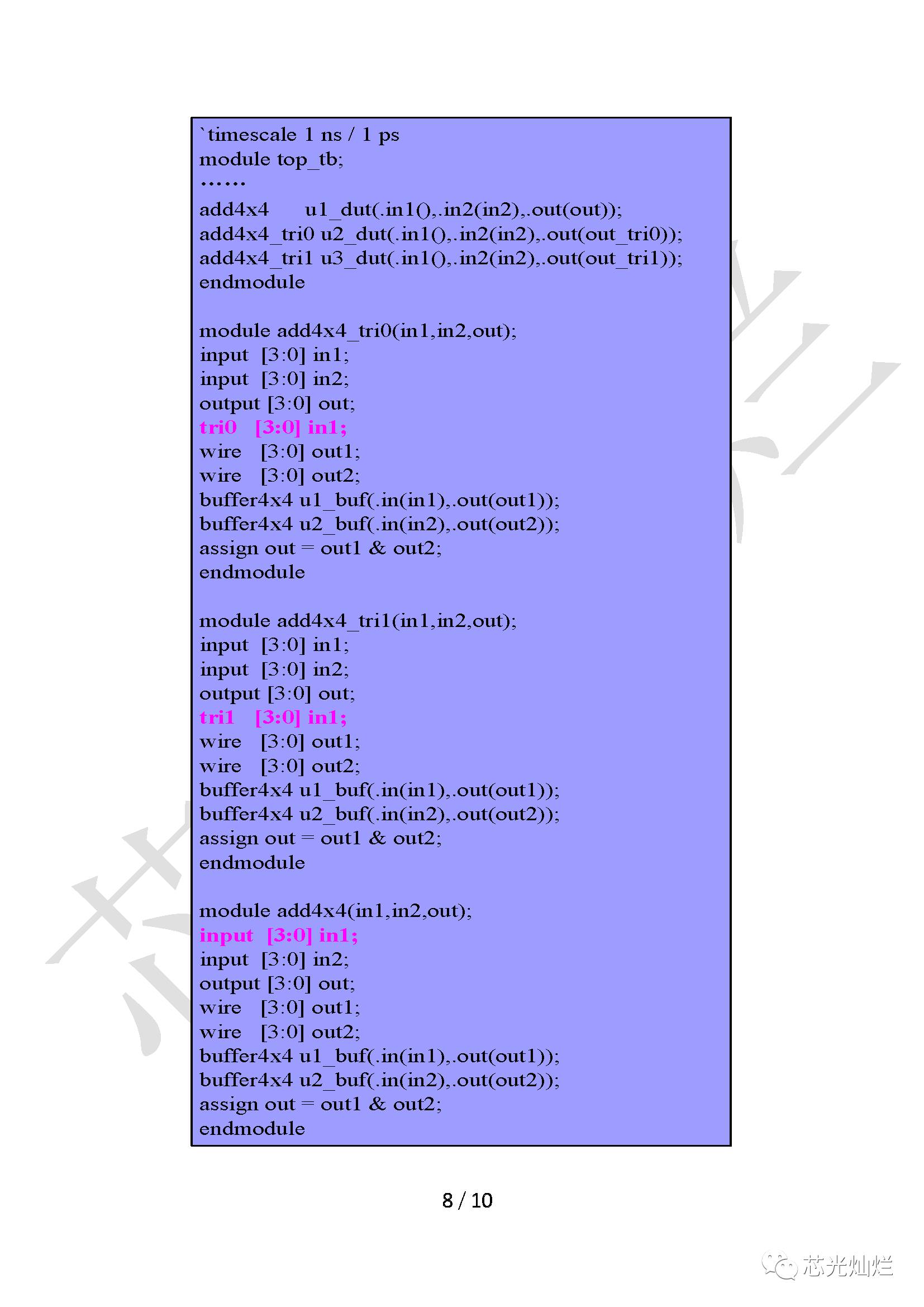

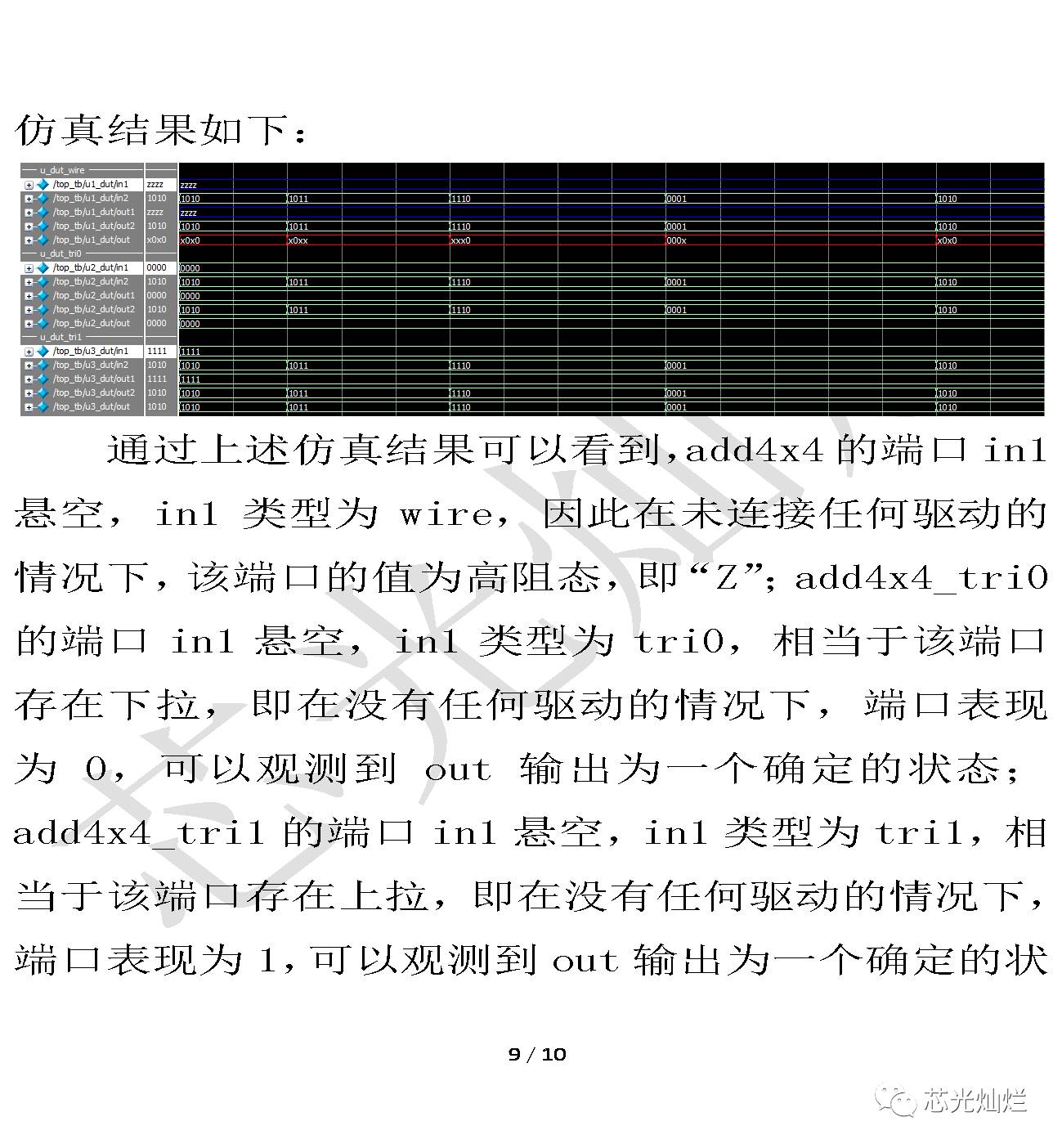

4>输入端口没有连接或者无驱动;

更多资讯,请关注下方二维码!