1、代码

`timescale 1ns / 1ps module pulse_synchronizer( input clk1, input clk2, input rstn, input pulse_in, output pulse_out ); reg reg1_clk1; always @(posedge clk1 or negedge rstn) begin if(!rstn) begin reg1_clk1 <= 1'b0; end else begin if(pulse_in) reg1_clk1 <= ~reg1_clk1; else reg1_clk1 <= reg1_clk1; end end reg reg1_clk2,reg2_clk2,reg3_clk2; always @(posedge clk2 or negedge rstn) begin if(!rstn) begin {reg1_clk2,reg2_clk2,reg3_clk2}<=3'b000; end else begin {reg1_clk2,reg2_clk2,reg3_clk2}<={reg1_clk1,reg1_clk2,reg2_clk2}; end end assign pulse_out = reg2_clk2^reg3_clk2; endmodule

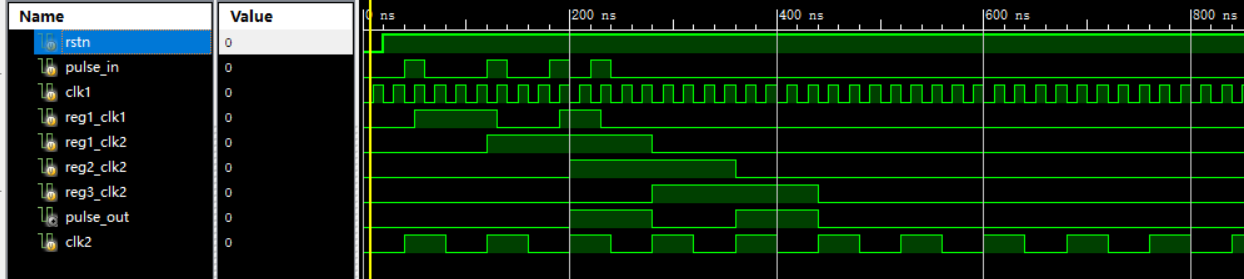

2、仿真波形