https://www.cnblogs.com/lyc-seu/p/12441366.html

一、同步电路和异步电路的优缺点

同步电路:

优点:

(1)EDA友好,EDA工具可以保证电路系统的时序收敛,有效避免了电路设计中的竞争冒险现象;

(2)由于触发器只有在时钟边缘才改变值,很大限度地减少了整个电路受毛刺和噪声影响的可能。

缺点:

(1)由于时钟网络连线长度和负载不同等原因,存在时钟偏斜(clock skew)问题,影响电路时序;

(2)为了解决时钟偏斜问题,时钟树综合需要插入大量延迟单元,使得电路面积和功耗大大增加;

(3)同步电路还受到时钟抖动(clock jitter)的影响。

异步电路:

优点:

(1)具有低功耗的特性,同步电路在同一全局时钟下工作,时钟工作频率必须满足最大负荷的要求,造成功耗浪费。异步电路则由数据驱动,仅在需要处理数据时才消耗能量,具有低功耗的潜力。随着如今电路规模指数级增长,维持全局时钟的高速翻转的功耗占系统功耗的比例越来越大。

(2)模块化特性突出,异步电路因为使用握手信号进行模块间的通信,模块互连后的功能不会受到各个模块内部延时的影响。

(3)不存在时钟偏斜问题。

(4)好的电磁兼容性,异步电路没有类似同步电路在特定时刻上的瞬时大电流,仅仅产生在一些时间分布的小电流峰值,辐射功率也小。

(5)有潜在的高性能特性,同步电路工作需要考虑电路的最坏情况延迟,而异步电路的性能则由电路的平均延迟决定,理论上比同步电路可以达到更高的速度。

缺点:

(1)设计复杂,缺乏EDA工具的支持。

二、同步单比特信号的几种方法

1、电平同步器

对于上面的双锁存器法,如果a_clk的频率比b_clk的频率高,将可能出现因为dat变化太快,而使b_clk无法采样的问题。即在信号从快时钟域向慢时钟域过渡的时候,如果信号变化太快,慢时钟将可能无法对该信号进行正确的采样,所以在使用双锁存器法的时候,应该使原始信号保持足够长的时间,以便另一个时钟域的锁存器可以正确地对其进行采样。

2、边沿同步器

如果我们需要用跳变沿而不是电平又该怎样处理呢,在电平同步器之后再加一级触发器,用第二级触发器的输出和第三级触发器的输出来进行操作。这种结构叫做边沿同步器。

always @ (posedge Clk)

begin

inputs_reg1

<= inputs;

inputs_reg2

<= inputs_reg1;

inputs_reg3

<= inputs_reg2;

if

(inputs_reg2 == 1'b1 && inputs_reg3 == 1'b0)

begin

...

end

...

end

以上两种同步器在慢时钟域信号同步入快时钟域时工作的很好,但是反过来的话,可能就工作不正常了。举一个很简单的例子,如果被同步的信号脉冲只有一个快时钟周期宽,且位于慢时钟的两个相邻跳变沿之间,那么是采不到的。这时就需要采用脉冲同步器。这种同步器也是由3个触发器组成,同时需要对发送信号做一些处理。

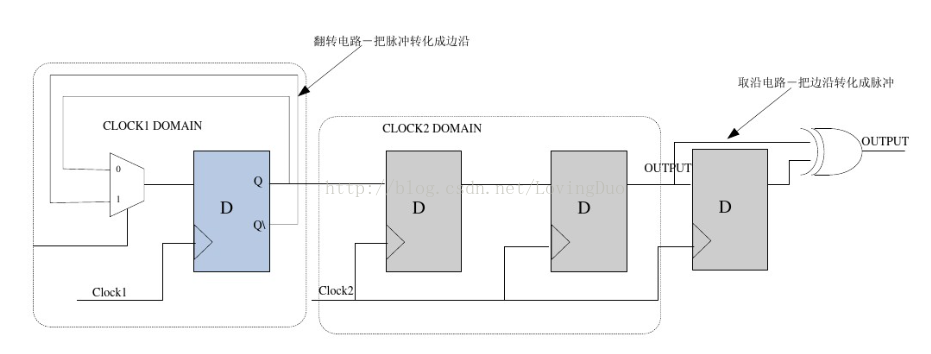

3、脉冲同步器

https://blog.csdn.net/lovingduo/article/details/77723219

脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路(下图)。每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲.

脉冲同步器的基本功能是从某个时钟域取出一个单时钟宽度脉冲,然后在新的时钟域中建立另一个单时钟宽度的脉冲。脉冲同步器也有一个限制,即输入脉冲之间的最小间隔必须等于两个同步器时钟周期。如果输入脉冲相互过近,则新时钟域中的输出脉冲也紧密相邻,结果是输出脉冲宽度比一个时钟周期宽。当输入脉冲时钟周期大于两个同步器时钟周期时,这个问题更加严重。这种情况下,如果输入脉冲相邻太近,则同步器就不能检测到每个脉冲。

4、双握手法:https://www.cnblogs.com/wt-seu/p/12929973.html

三、同步多比特信号的几种方法

1、异步FIFO

2、握手协议,如双握手法(Req、Ack):https://www.cnblogs.com/wt-seu/p/13418878.html

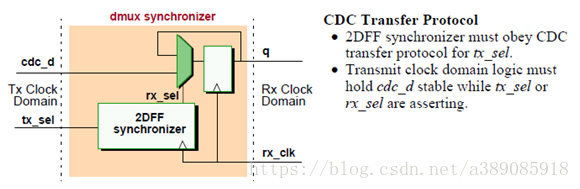

3、DMUX

对于多bit的data信号,还可以使用使能技术,也就是通过一个使能信号来判断data信号是否已经稳定,当使能信号有效的时候说明data处于稳定状态,在这种情况下终点寄存器才对信号进行采样,可以保证没有setup/hold违例。而使能信号一般使用double FF的方法来进行同步。下面是DMUX的同步示意图: