1.时序逻辑电路由两个部分组成,为什么前面介绍了触发器,就是为了这里的时序逻辑电路做准备的。时序逻辑电路的两部分一个是组合逻辑电路,一个存储部分。存储部分就是触发器组成的。相应的时序逻辑电路的输出也就由两个部分组成,一个是组合逻辑电路的输出,另个一个是存储部分的输出。还有一点需要注意的是,时序电路估计比较复杂,不太容易画出逻辑图,因此只能抽象地画出两个组成部件。

2.存储器是由多个存储单元组成的,这里的存储单元就是触发器。

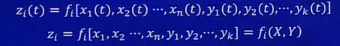

3.假设某一个时序逻辑电路有n个外输入,m个外输出,k个存储单元,那么某个 i 外输出为

从这个等式可以看出一些思想:为什么说数字电路的设计和系统是属于计算机编程底层的知识?编程时,工作人员只需要编好相应的程序,逻辑功能,具体怎样实施,怎样简洁地实施,这都和编程人员无关。逻辑功能抽象到底,就是多元的函数等式,有众多的自变量,因变量。在这里,我可不可以发散的想一下,为什么说算法挺重要,估计算法就是直接将逻辑功能的这种函数等式表达出来,而入门级别的程序员干的活只是一个频繁地调用别用设计好的东西,没什么技术含量,只要知道有什么,自己需要什么,最后直接调用即可。但是,现在作为一个学习数字电路的人来说,可能到最后,自己依旧无法设计出符合要求的数字电路,但是你能清楚这其中的运作机制,那有助于对上层运作的了解。抛开上面的题外话,每一个输出都是所有输入的函数,计算机还是一个数学为核心的学科。这里还有一点,为什么要有那么多的输出,我可以理解为每一个输出代表着一个逻辑功能,同一个电路中,越多的输出可以减少电路的成本,也可以展现更多的逻辑功能。

4.仔细地看下面的这张时序逻辑电路的抽象图,我除了想说触发器在时序逻辑电路中起到了存储作用外,还将触发器反馈的特点清晰地表现了出来。时序逻辑电路的两个组成部件联系很紧密,组合逻辑电路给存储器提供了内输入,存储器又反馈给时序逻辑电路整个外输入。

5.在时序逻辑电路中,有这么几个概念,外输入,内输入,外输出,内输出。这几个概念不弄清楚,对于时序逻辑电路的理解就不会深刻。存储器是由内输出得到的内输入信号,内输入信号要反馈到时序逻辑电路中,作为整个电路的部分激励信号来看待。内输入和内输出的命名都是针对时序逻辑电路而言的,这种命名对存储器不利。

我们回过头来再看当时的方程 ,这个方程是即可输出方程,意味着所有的外输入和内输入一确定,那么时序逻辑电路的输出就确定了,内输入和外输入两者间是分开来看的,,从某种程度上来说,内输入是由外输入决定的,内输入本质上是反馈。

,这个方程是即可输出方程,意味着所有的外输入和内输入一确定,那么时序逻辑电路的输出就确定了,内输入和外输入两者间是分开来看的,,从某种程度上来说,内输入是由外输入决定的,内输入本质上是反馈。

为什么时序逻辑电路的外输出是即刻输出方程,这里面是否和时序逻辑电路的逻辑功能有关系?

6.现在仔细研究存储器,在整个时序逻辑电路中,组合逻辑电路较为死板,研究的意义不大,但是信号在存储器里面的回路就比较值得研究了。相较于外输出的即刻输出方程,存储器的方程称之为激励方程或驱动方程。触发器由k个存储单元组成,那么就存在k个驱动方程,