数据分配器

1.数据分配器是数据选择器的逆过程。

2.1-4路的数据分配器,这是个设计组合电路的过程。首先,我们先明确1-4路的数据分配器的功能:一路串行输入数据,输出四路数据。控制信号(地址信号)地址信号是和一路串行输入数据连在一起构成函数表达式么?

数据比较器

1.顾名思义,这个逻辑电路就是用来进行两个数值间的比较的,比较的结果有三种,大于,小于,等于。每次比较两个数值时,总会在这三种情况中出现一种。这说明逻辑电路的设计过程中要注意的问题,每一个逻辑电路都是由不同的输入变量和不同的输出变量组成,然后要明确输入变量有哪几个,输出变量有哪几个,同时,每一个输出变量的函数表达式都是由所有输入变量组成的,而这些逻辑函数的表达式很多时候就是之前常见的逻辑功能,同或,异或.......最常见的写逻辑函数表达式的方法就是依照真值表写标准的与或式(最小项表达式)。这里还要说明的一点就是,当有多个输出时,在画逻辑图是需要共用所有输入,所有的输出在同一张逻辑图上表示出来。

2.前述的是两个一位的数值之间的比较,每一个都是取0或1。接着又谈论到两个二位的数值之间的比较,所有的输入数据均是二进制的0或1,在计算机里,所有的数据均是用二进制来表示的,无论是文字,图片还是数值均是用二进制代码来表示的,这里进行数制上的比较,一定是计算机将十进制的数字转变成了二进制,所有的数据输入计算机时都要被转化成二进制的编码,区别在于数值被转化后,是具有权位的二进制数码。

3.一位的数值比较器是两个一位的数值在比较,二位的数值比较器是两个二位的数值在比较,以此类推,随着位数不断的增加,再通过真值表的方法来比较显得很麻烦。

第二次理解数据比较器和校验器

数据比较器

1.数值比较器最常见的是对两个数值A和B大小进行比较,但是我们是不清楚A,B的具体数值,或者说,任意两个数值间进行比较,比较过后会产生三种结果。这样一来,数值比较器的逻辑功能就是对输入的不同数值进行比较,并将得到的结果输出。在这里,我们相当于重新回顾了组合逻辑电路的设计,明确好电路中的输入和输出,然后列出真值表,再依据最小项法写出每个输出的函数表达式,最后根据函数表达式画出逻辑图。

2.本小节最开始是介绍了两个一位数值间的比较的例子,输入变量是两个A和B,由于是在计算机内的数值比较,A和B必然是二进制数,这样输入变量的所有取值就可以确定。两个数值间进行对比只有三种情况,每次对比后,必然是三种情况中的一种。这样三种情况作为三种输出,每次只有一种输出被输出,被输出的输出标记为1,其余的标记为0。这样这个组合逻辑电路的分析过程就完成了第一步,将所有的输入,和输出全部填入真值表。我们只需按照符合条件填满真值表,至于怎么实现是下一步的事,只要我们将真值表写对即可。按照最小项法,正确的真值表自然带来能够完成要求的逻辑表达式。在真值表中,三种输出间是有联系的,相当于存在约束,但是在写函数表达式时,每个输出都拥有自己的表达式,每个表达式都和所有的输入变量间构成关系,表达式之间并没有任何关系。最后在画出逻辑图时,又将所有的输入,输出合在一张图中。

3.第二个例子,开始增加两个比较数值的位数,增加难度,但是输出变量仍然是三种情况,就是对比的例子多了许多,24=16,有16种输入变量,会增加工作量,但是本质并没有什么变化。在输入变量中,不同的变量可以是没有联系的,如A和B,也可以是有联系的,A1A0,B1B0,这里说是有四个输入变量。本质上来说,四个变量间任意输入,但是我们人为地将所有输入间建立了联系,这些联系最后通过逻辑表达式表现出来,逻辑图的连线表现出来。

4.随着两个数值的位数的增加,真值表的绘制越来越困难,这样通过比较两个数值间的有权位的二进制数就是不合理的。要知道越是复杂的过程越是不合理。初始的两个例子均是采用的相同的解决思想,这样是无法解决过程的复杂性,只有换个思路才行。通过逐步对比两个数值间的高位,来判别两个数值的大小。这里产生一个问题,是不是每一位的比较,都要配备有三个输出,或者说这三个输出可以共用。

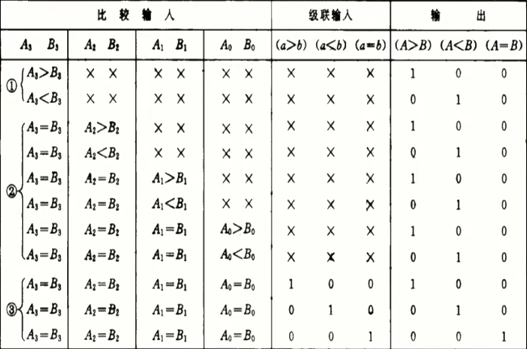

5.中规模7485就是逐级比较高位来得出两个数值大小的数值比较器。四位二进制的数值比较器,这是两个四位的数值在进行比较。

级联输入:因为比较器所能比较的位数并不多,所以有时需要多个比较器,这个时候最低位的比较器就需要往上传递信息,称为级联输入。

根据中规模7485的逻辑符号来理解级联输入,逻辑符号中上一行是两个四位的数值,如果是六位的两个数值的话,除了上一行的高四位,还存在着低二位的比较的,如果高位比较不出结果的话,这时候不着急输出结果,还需要看低位的比较结果,这时候,低位的比较结果就需要输入级联输入,高位和地位对比完了之后,在输出。一种要注意一点,所有的高位比较不出来时,才需要级联输入低位的结果。

6.讲解7485的逻辑图时,某一级门电路的逻辑表达式的简化出现了这样的情况,不是很理解,(AB)'A=B'A这是运用了怎样的原理?

最原始的表达式是F={(AB)'A+(AB)'B}'={B'A+A'B}',这里能不能采用反演公式来简化成这样,反演公式有些遗忘了。

7.中规模7485四位数值比较器的真值表

仔细看这张真值表,输入端写着比较输入,而非我们之前所习惯的二进制数的输入,但是我觉着这只是一个省略地写法,重点突出输出是由输入数值间的大小判别得出来的。真值表的输入是对应高位间的大小判别,从高位到低位,逐级递减,只要有明确的大和小,那么就会输出结果。如果相等,那就往下一级进行比较,以此类推,如果所有的高位都是相等,这时候就需要级联输入,级联输入的三种结果,决定了最终的输出。我想.中规模7485四位数值比较器还是建立在一位数值比较的器的基础上得来的,最开始地输入不可能是一个判别好的结果,我说的是从最高位开始的输入。

8.重点讲解级联输入的作用。

举例为两个八位的二进制数值的比较。一谈到这种多位的数值比较器,至少是四位开始,如果是四位的直接配备一个中规模7485数值比较器,自身就是两个四位比较,没有级联输入,各种结果由三个输出端直接输出。如果高于四位,那就是由多个中规模7485组成,多位的数值比较从高四位的7485数值比较器开始。多位数值比较一定要想到对应位之间的比较,高位全都相等,就将级联输入得出最终结果。

级联输入的三中情况又是怎么来的?是由低位的7485数值比较器的结果得来的.

奇偶校验位的产生和校验电路

1.奇偶校验校验数据传送对错的一种方法,这种方法简单有效,但是不能对所有传输错误的数据进行校验,仅仅校验数据的奇偶性,根据数据的奇偶性来断定数据的传输是否正确。奇偶校验位如果是一位的奇偶校验位,对于传输数据只有一位发生改变导致传输数据的奇偶性发生变化,通过奇偶校验我们是可以判别的,但是如果是两位发生了改变,那么这个方法是无法检验出来的,而且但一位出错时,这种方法也没法检验出发生错误的那一位在哪儿。总之,这是一种很粗糙的检验手段。

奇偶校验只能校验对还是错,错了没法找出哪里出错进行检错,只能告诉发送方重新发送数据。

第一步要生成奇偶校验位,生成的校验位和数据位合起来,如果是奇校验,那么合起来的位数中,1的数目是奇数,如果是偶校验,那么校验位和数据位中,1的数目是呈现偶数个。

从数据位如何产生校验位,这是一个问题,还有一个问题就是如何校验,传输到位后,如何对传输来的数据进行奇偶校验,它的奇偶性是怎样的?这两个问题实际上是同一个电路,所以经常称为奇偶校验与产生电路。奇偶校验位就是在数据位上再加上一位,通过在奇偶校验位设置为0或者1,使得我们构成奇校验或者偶校验。

奇偶检验位的取值原则是:采用奇校验(采用哪种校验是人们提前设定好的),校验位和数据位中,1的个数是奇数个。反之,偶检验是校验位和数据位的整个代码中,1的个数是偶数个。

奇校验和偶校验,它们的校验位的取值是相反的。

讨论校验位的产生电路:求解产生电路本质上还是回到设计逻辑电路的老路上,