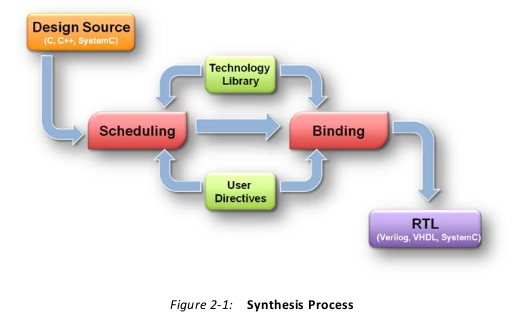

High-Level Synthesis transforms a C, C++ or SystemC design specification into a Register

Transfer Level (RTL) implementation that in turn can be synthesized into a Xilinx Field

Programmable Gate Array (FPGA).

To perform this task High-Level Synthesis, does the following:

•First elaborate the C, C++ or SystemC source code into an internal database containing

operators.

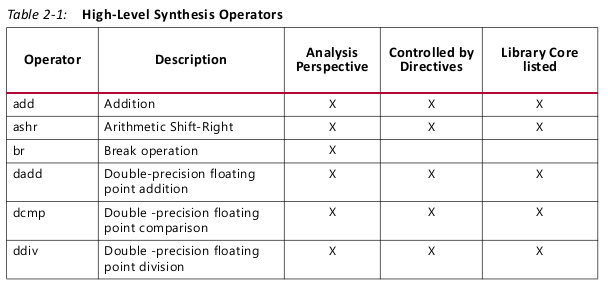

The operators represent operations in the C code such as additions, multiplications, array reads, and writes.

•During synthesis, High-Level Synthesis maps the operators to cores from the

High-Level Synthesis library.

Cores are the specific hardware components used to create the design (such as

adders, multipliers, pipelined multipliers, and blockRAMs)

Reference:

https://www.xilinx.com/support/documentation/sw_manuals/xilinx2013_3/ug902-vivado-high-level-synthesis.pdf