https://mp.weixin.qq.com/s/gNN2eiJnr9N02xdZVQceDQ

相较于GSL层对物理连接的建模,RTL层提高了一个抽象层次:

- 把物理的触发器提取为抽象的寄存器数据类型,简化了从触发器中存取值的操作。

- 把物理的门和开关原语的逻辑,提取为操作符号& | ~等,甚至常见的逻辑也提取为操作符号,如移位,相等判断等;把相关物理模块之间的逻辑联系,转换为寄存器之间值的运算和操作关系;

程序 = 数据 + 算法

使用数据类型(寄存器)描述数据,使用各种操作符把数据关联成表达式(expression),再使用赋值把表达式关连成语句(statement),这就组成了程序的全部要件。

从另外一个角度,每一个模块即是一个 输入、处理、输出的完整系统,输入和输出的数据类型为寄存器,处理使用操作符和赋值来描述。这样也构成了描述模块的全部要件。

所以,相较于GSL,RTL不仅提高了抽象层次,提升了表达能力和表达效率,而且构成了一个描述逻辑的完备系统。

事实上(使用Verilog的语汇),最简的情况下,只使用reg和module即可完成建模的任务,无论是assign还是always都可以转换为所属module的子module。

但是这样建立的模型略显复杂,且表达效率低,比如module虽然可以表达对输入的依赖,但是却不能像always那样,明确的表达对posedge/negedge的依赖。

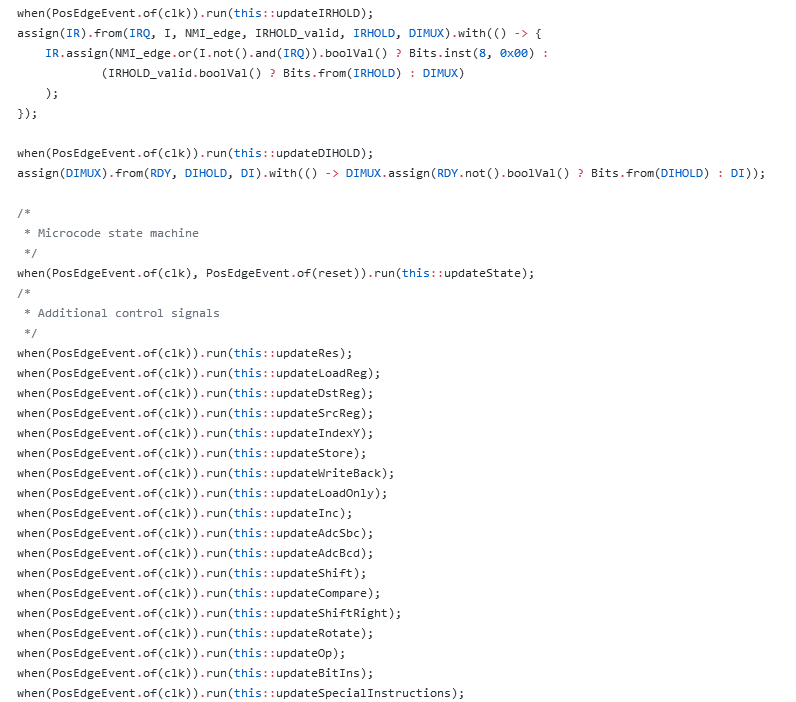

所以,jchdl对RTL层的建模,参考了Verilog和SystemVerilog:

- 支持的数据类型有bit/bits/reg;

- 支持Verilog提供的一部分操作符;

- 支持Verilog的posedge/negedge和changing事件;

- 支持Verilog的assign/always代码块;

一. Bit

Bit可以理解为线。但使用二值逻辑,只支持0, 1两个值。

二. Bits

Bits为一组线,由多个Bit组成;

Bit和Bits支持assign操作,不支持set;

三. Reg

寄存器数据类型,有多个Bit组成;

只支持set操作,不支持assign;

四. Event

RTL建模使用事件驱动模型,支持三种事件:posedge/negedge/changing;

比如assign代码块:assign a = b & c; 其中a依赖于b和c的变化事件(Changing Event),如果b和c的值发生变化,则会经由处理逻辑(相与),反映到a的变化上。

always代码块则会明确描述所依赖的事件,即敏感表。

五. Block

参考Verilog,目前支持两种最基本的代码块,即assign和block;

六. Module

概念上对应Verilog中的module。模块描述了一个输入经过处理逻辑转换为输出的基本单元。

模块可以有子模块和父模块,组成模型结构(hierarchy)。