https://mp.weixin.qq.com/s/e8vJ8claauBtiuedxYYaJw

实现可以动态索引的表。

参考链接:

https://github.com/ucb-bar/chisel-tutorial/blob/release/src/main/scala/examples/Tbl.scala

1. 引入Chisel3

2. 继承自Module类

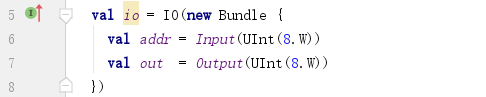

3. 定义输入输出接口

创建各项输入输出接口。

val addr = Input(UInt(8.W))

a. 使用8.W表示位宽为8位;

b. 使用UInt创建无符号整型数;

c. 使用Input/Output表示接口方向;

d. val 关键字表明定义的变量是所属匿名Bundle子类的数据成员;

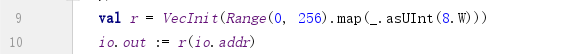

4. 内部连接

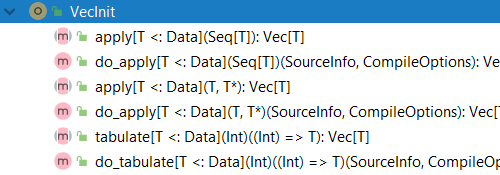

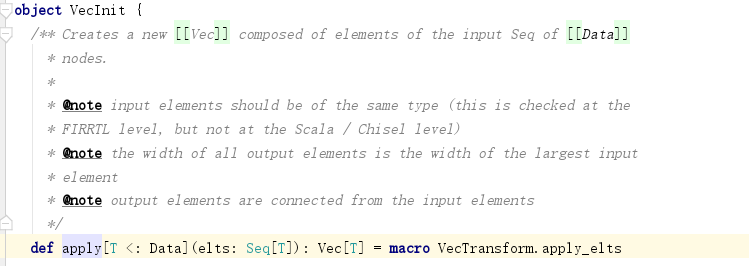

1) 创建一个向量,并赋予初值:

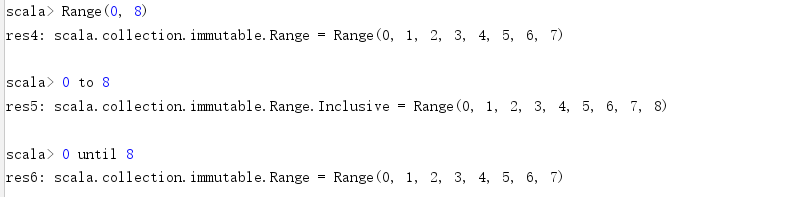

其中:Range(0, 256).map(_.asUInt(8.W))

a. 创建一个[0, 256)的Range,不包含256(exclusive)。

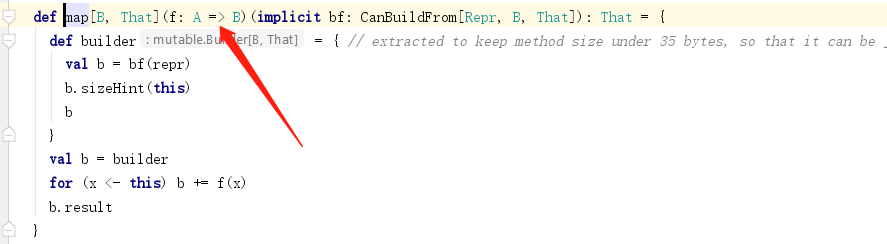

b. 调用Range的map方法,针对Range的每一个元素执行map的参数所指代的方法:

c. 转换函数f: A => B

定义为:

_.asUInt(8.W))

其中“_”指代传入的参数,更容易理解的写法为:

(a) => a.asUInt(8.W))

亦即,针对每一个传入的参数a(这里a是Range内的每一个值),调用a.asUInt(8.W),并将其返回值作为返回值。

2) 索引向量并输出对应值:io.out := r(io.addr)

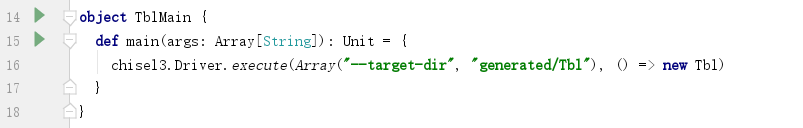

5. 生成Verilog

可以直接点运行符号运行。

也可以使用sbt shell执行:

略

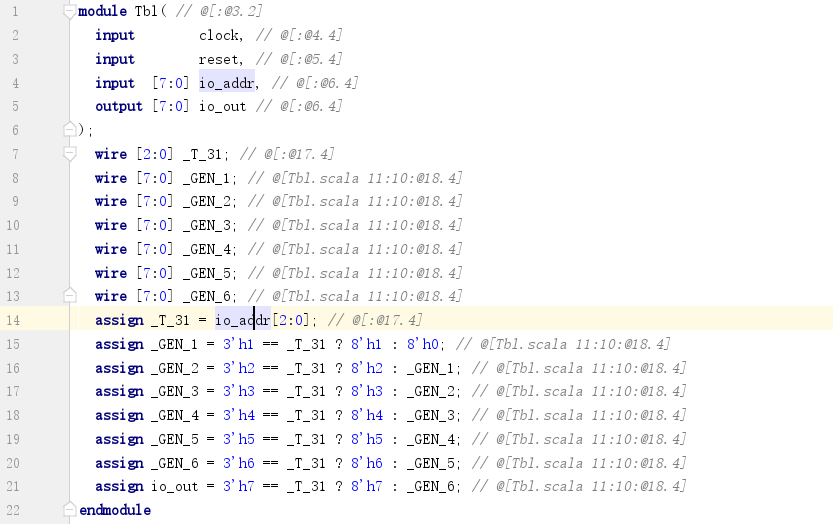

生成Verilog如下:

6. 测试

略

7. 附录

Tbl.scala:

import chisel3._

class Tbl extends Module {

val io = IO(new Bundle {

val addr = Input(UInt(8.W))

val out = Output(UInt(8.W))

})

// val r = VecInit(Range(0, 256).map(_.asUInt(8.W)))

val r = VecInit(Range(0, 8).map((a) => a.asUInt(8.W)))

io.out := r(io.addr)

}

object TblMain {

def main(args: Array[String]): Unit = {

chisel3.Driver.execute(Array("--target-dir", "generated/Tbl"), () => new Tbl)

}

}