https://mp.weixin.qq.com/s/OtiQnE52PwdCpvmzJ6VFnA

奇偶发生器。统计输入中1的个数,如果为偶数则输出0,奇数则输出1。

参考链接:

https://github.com/ucb-bar/chisel-tutorial/blob/release/src/main/scala/examples/Parity.scala

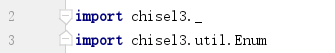

1. 引入Chisel3

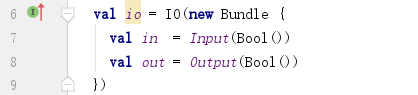

2. 继承自Module类

3. 定义输入输出接口

创建各项输入输出接口。

这些接口Bool型数:val in = Input(Bool())

a. 使用Bool()创建布尔型数,位宽为1位;

b. 使用Input/Output表示接口方向;

c. val 关键字表明定义的变量是所属匿名Bundle子类的数据成员;

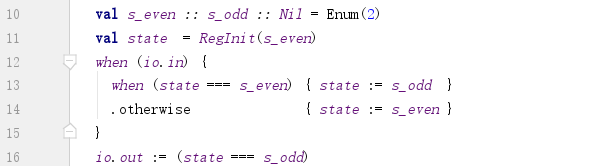

4. 内部连接

使用state寄存器来存放状态,形成一个状态机。

1) 使用RegInit()创建一个初值为s_even的寄存器;

2) when()嵌套使用

3) 状态枚举的创建:val s_even :: s_odd :: Nil = Enum(2)

a. Enum(2)创建一个包含2个元素的枚举;

b. 把这两个枚举元素逐个赋值给s_even和s_odd;所以这里同时声明和赋值了两个变量;这是Scala支持的一种定义方法。

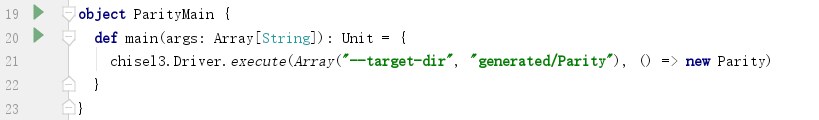

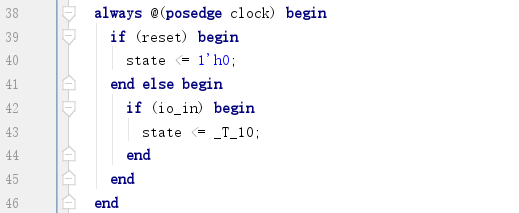

5. 生成Verilog

可以直接点运行符号运行。

也可以使用sbt shell执行:

略

生成Verilog如下:

6. 测试

略

7. 附录

Parity.scala:

import chisel3._

import chisel3.util.Enum

class Parity extends Module {

val io = IO(new Bundle {

val in = Input(Bool())

val out = Output(Bool())

})

val s_even :: s_odd :: Nil = Enum(2)

val state = RegInit(s_even)

when (io.in) {

when (state === s_even) { state := s_odd }

.otherwise { state := s_even }

}

io.out := (state === s_odd)

}

object ParityMain {

def main(args: Array[String]): Unit = {

chisel3.Driver.execute(Array("--target-dir", "generated/Parity"), () => new Parity)

}

}