https://mp.weixin.qq.com/s/bSrM-wLRn7O_75xYKeoaEQ

Chisel中的基本数据类型,不是Verilog中的Wire和Reg。Wire和Register只是数据的容器,而非数据本身。所以Chisel中的数据类型抽象层次更高一些,更关注数据的行为和组织形式的异同。

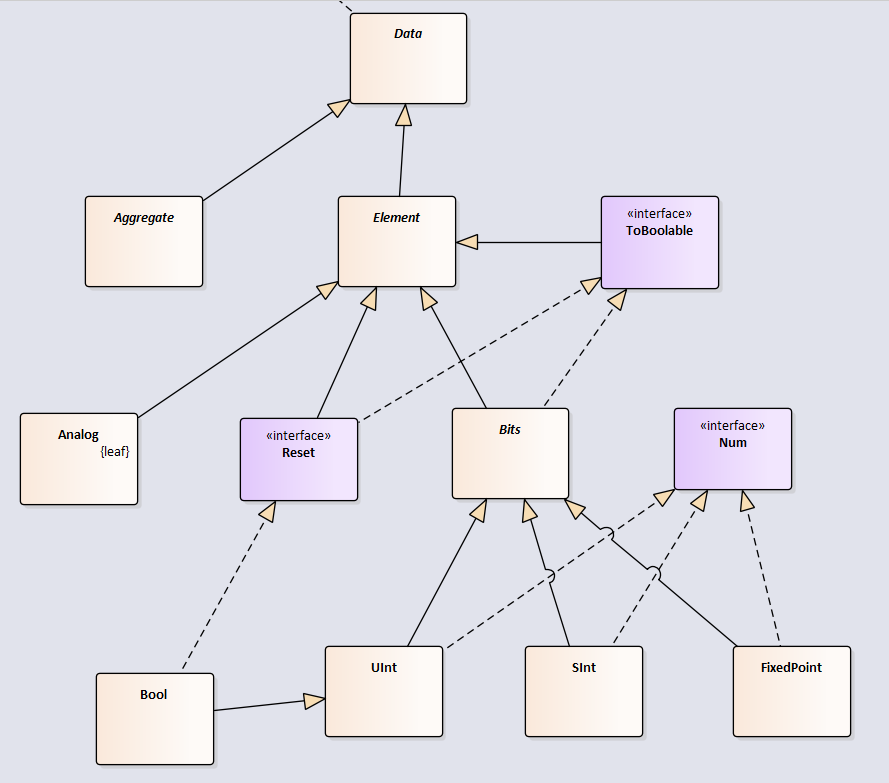

基本数据类型的类图如下:

其中:

1. 实线箭头为继承父类(extends);

2. 虚线箭头为实现接口(with);

3. 倾斜字体的类为抽象类(abstract);

4. 标注为叶子(leaf)的为最终类(final);

参考链接:

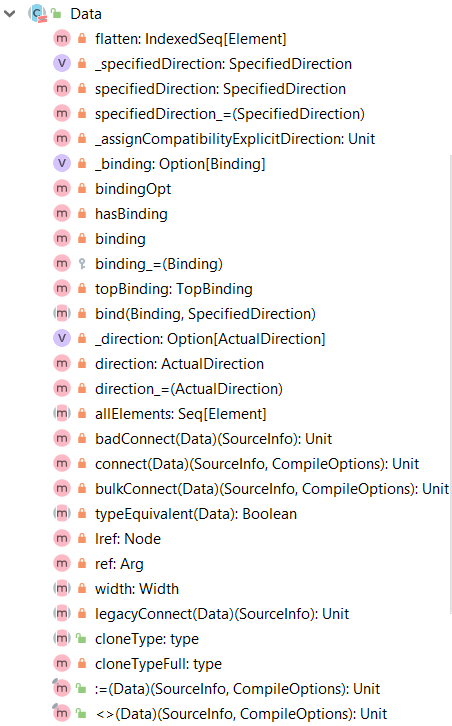

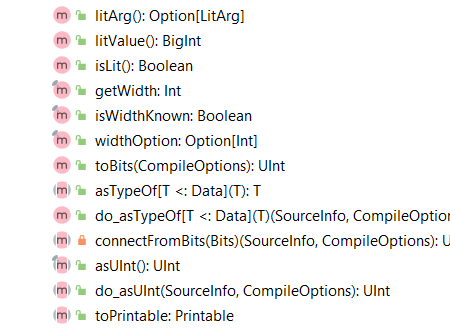

1. Data

所有数据类型的父类,包含了基本数据类型和复合数据类型的共同的属性和方法。

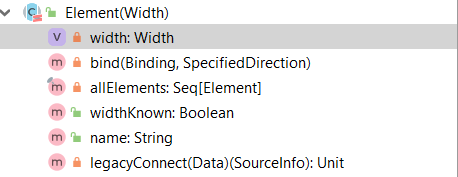

2. Element

基本数据类型的父类

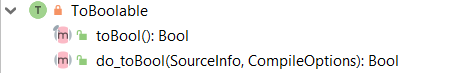

3. ToBoolable

可以转换成布尔型的类型。在Verilog中wire和reg类型都可以作为真假判断条件。

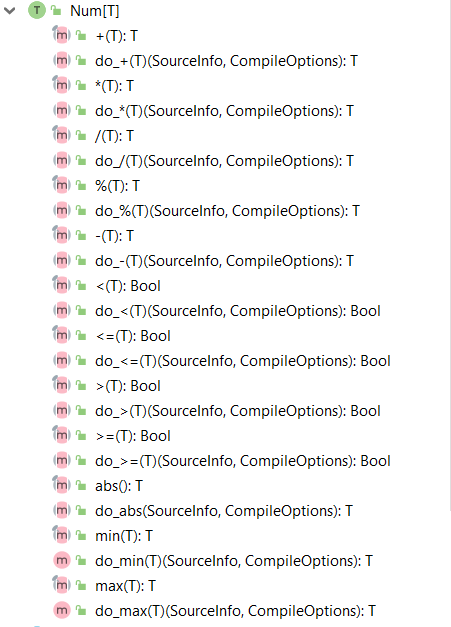

4. Num

数字类型的接口。包含数字的基本运算和比较方法。

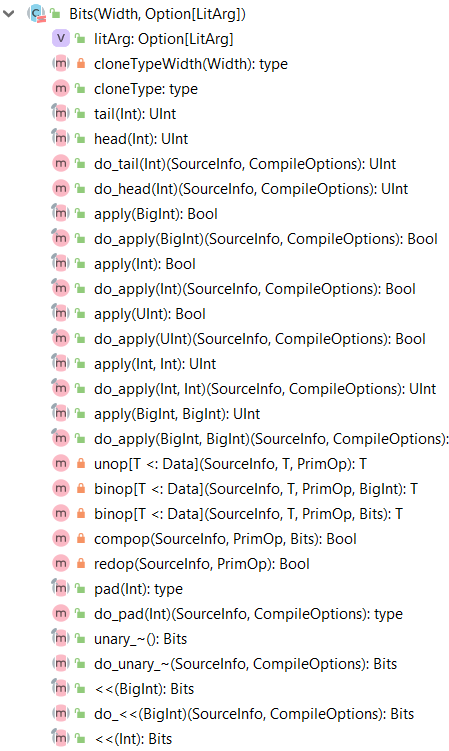

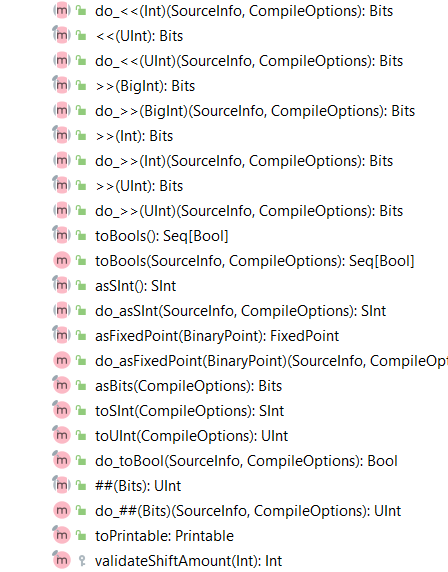

5. Bits

所有的数值,最终都要以二进制比特组的形式表达,Bits就代表这个比特序列。包含位选择和各种位操作。

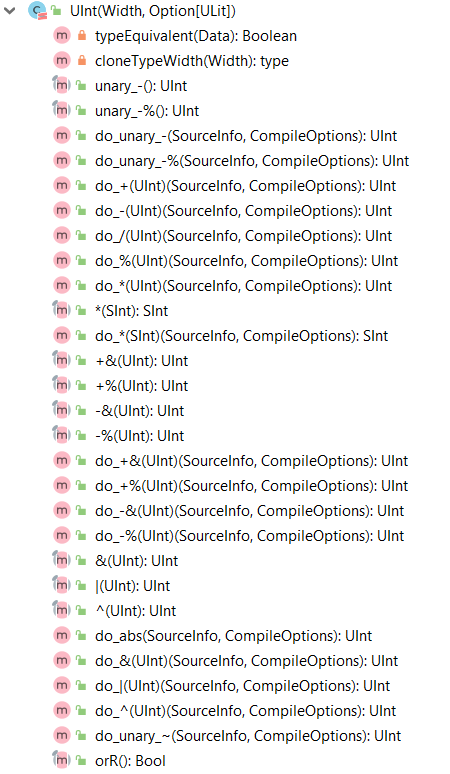

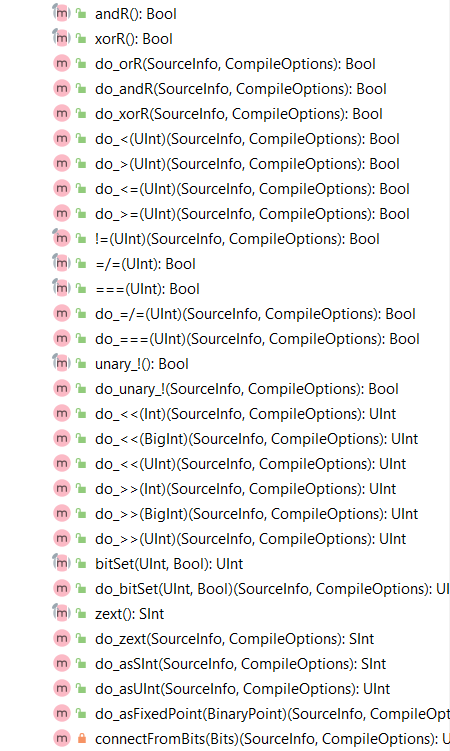

6. UInt

无符号整型数。

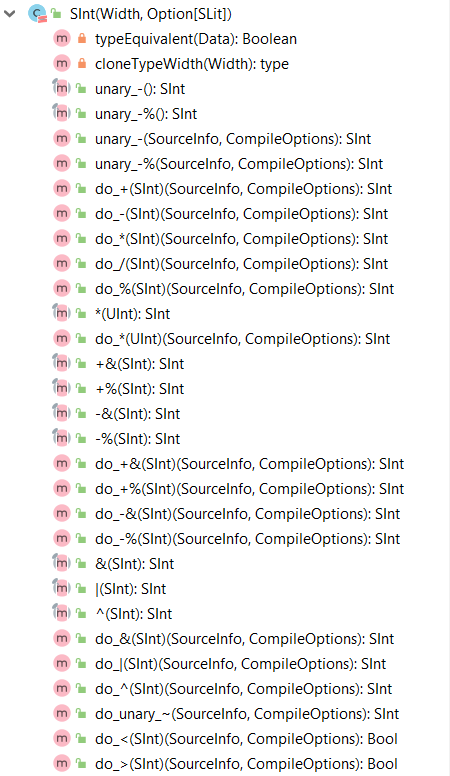

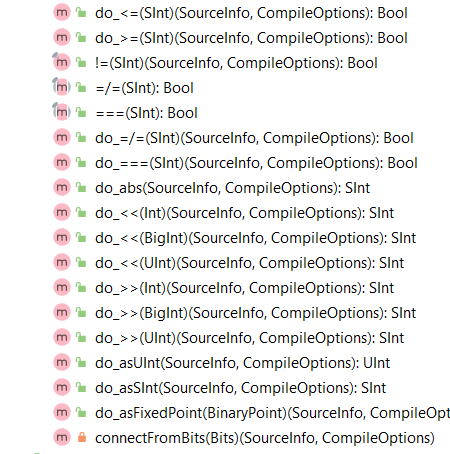

7. SInt

有符号整型数

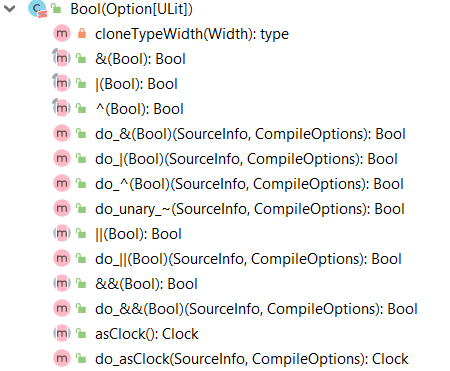

8. Bool

布尔型

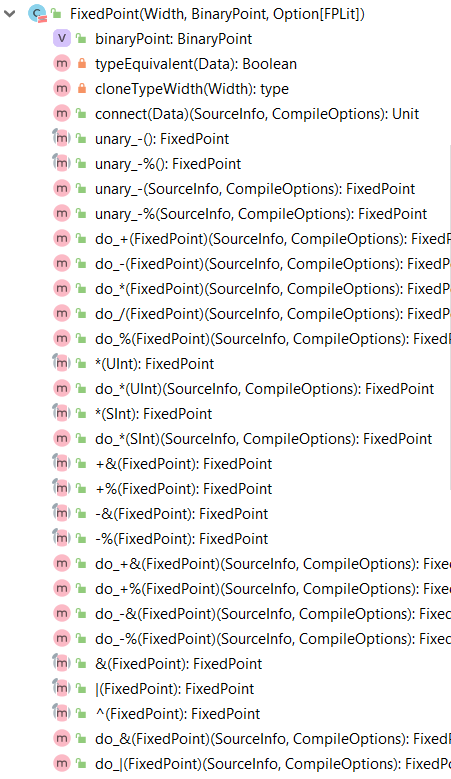

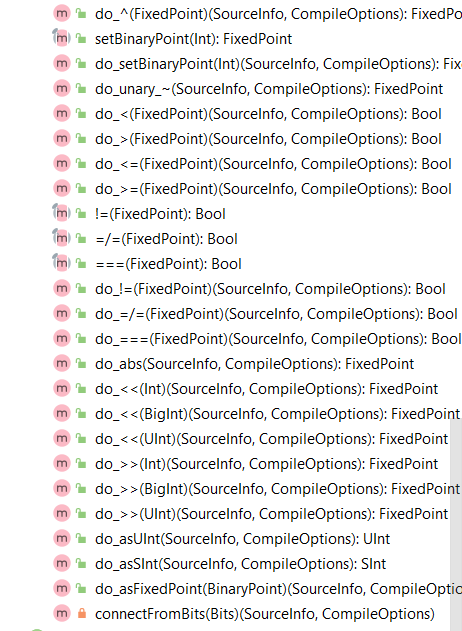

9. FixedPoint

定点数。

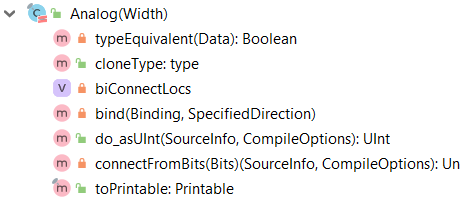

10. Analog

Data type for representing bidirectional bitvectors of a given width.

Analog support is limited to allowing wiring up of Verilog BlackBoxes with bidirectional (inout)

pins. There is currently no support for reading or writing of Analog types within Chisel code.