APB(Advanced Peripheral Bus),外围总线的意思。该总线协议是ARM公司提出的AMBA总线结构之一,几乎已成为一种标准的片上总线结构。APB可以向上连接至AHB-Lite和AXI总线。APB的每个传输都在时钟上升沿处罚,每个传输至少消耗两个时钟周期。Amba 3新加入了PREADY和PSLVERR。

1、Amba 3 APB的信号列表如下表:

| Signal | Source | Description |

| PCLK | Clock source | APB Clk |

| PRESETn | System bus equivalent | Reset. The APB reset signal is active LOW. This signal is normally connected directly to the system bus reset signal. |

| PADDR | APB bridge | Address. This is the APB address bus. It can be up to 32 bits wide and is driven by the peripheral bus bridge unit. |

| PSELx | APB bridge | Select. The APB bridge unit generates this signal to each peripheral bus slave.It indicates that the slave device is selected and that a data transfer is required.There is a PSELx signal for each slave. |

| PENABLE | APB bridge | Enable. This signal indicates the second and subsequent cycles of an APB transfer. |

| PWRITE | APB bridge | Direction. This signal indicates an APB write access when HIGH and an APB read access when LOW. |

| PWDATA | APB bridge | Write data. This bus is driven by the peripheral bus bridge unit during write cycles when PWRITE is HIGH. This bus can be up to 32 bits wide. |

| PREADY | Slave interface | Ready. The slave uses this signal to extend an APB transfer. |

| PRDATA | Slave interface | Read Data. The selected slave drives this bus during read cycles when PWRITE is LOW. This bus can be up to 32-bits wide. |

| PSLVERR | Slave interface | This signal indicates a transfer failure. APB peripherals are not required to support the PSLVERR pin. This is true for both existing and new APB peripheral designs. Where a peripheral does not include this pin then the appropriate input to the APB bridge is tied LOW. |

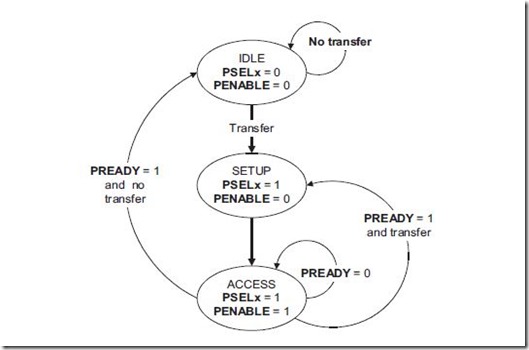

2、 APB总线的状态转移图

IDLE:状态机默认状态;

SETUP:有传输发生后就转到此状态,对应的PSELx被选中,该状态通常持续一个时钟周期,在下个上升沿进入ACCESS;

ACCESS:PENABLE信号使能,从SETUP到ACCESS,PADDR、PSELx、PWRITE、PWDATA的值须保持稳定不变。来自Slave的PREADY信号控制从ACCESS状态向下转变,PREADY=0,继续保持在ACCESS状态,延长ACCESS以等待Slave;PREADY=1,若没有其他传输,直接进入IDLE,若有后续传输,则直接进入SETUP状态。