第四章和第五章的硬件部分先跳过, 第六章的内容为p435~p486.

摘要

本章主要讲了存储器的层次结构. 寄存器 > L1 Cache > L2 Cache > L3 Cache > 内存 > 硬盘 > 网络.

以时钟周期来计算, 寄存器(0t) > L1~3 Cache(4~75t) > 内存(上百t) > 硬盘 (几千万t).

层次结构是基于"局部性"原理而构建的, 即程序相邻的代码访问的数据和指令是距离很近的, 这样层次结构才能发挥它的效果, 否则程序就会运行的很慢.

存储技术

缓存和内存

RAM(Random-Access Memory)分为SRAM和DRAM. SRAM不需要频繁的刷新保持数据, DRAM需要频繁的刷新才能保持数据, 但是一旦断电, 都会丢失数据.

| 每位晶体管数 | 相同访问时间 | 持续的? | 敏感的? | 相对花费 | 应用 | |

|---|---|---|---|---|---|---|

| SRAM | 6 | 1X | 是 | 否 | 1000X | 高速缓存存储器 |

| DRAM | 1 | 10X | 否 | 是 | 1X | 主存, 帧缓冲区 |

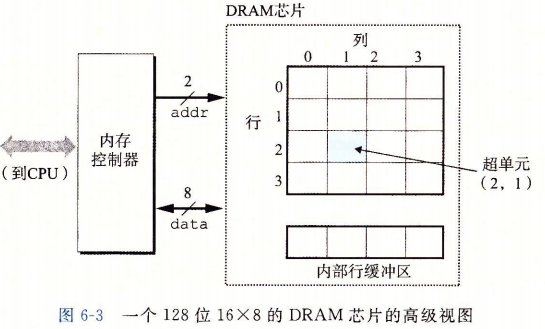

DRAM芯片以矩阵的方式进行访问, 分行号i和列号j. 如下的DRAM有16个超单元, 每个超单元存储8位数据, 总共存储16*8=128位数据.

地址访问需要2个引脚, 第一次行请求RAS(Row Access Strobe) 发送行号, 读取一行数据到行内缓冲区, 第二次列请求CAS(Column Access Strobe) 发送列号, 再从缓冲区中取出该列信息发送给Data引脚.

Data引脚需要8个引脚, 一次传输8位信息.

内存由多个DRAM芯片封装而成.

有很多更快的DRAM技术, 如FPM DRAM, EDO DRAM, SDRAM, DDR SDRAM(我们熟悉的DDR3, DDR4), VRAM.

DDR3有240个引脚, DDR4有284个引脚. DDR3最高支持2133MT/s, DDR4数据传输率也从2133MT/s起跳,最高速率在2013年的标准中暂定为4266MT/s.

CPU读写内存, 需要总线的传输, CPU -> 系统总线 -> I/O桥 -> 内存总线 -> 内存.

磁盘

缓存和内存为了速度, 都是易失类型, 断电后无法保存. 磁盘用的非易失类型.

ROM(Read-Only Memory)只读存储器, PROM(Programmable ROM)只能被编程一次, EPROM(Erasable Programmable ROM)需要光线进行擦除, 可编程1000次, EEPROM(Electrically Erasable Programmable ROM)可以直接在印制电路卡上编程, 可编程10^5次.

闪存(flash memory)基于EEPROM, 一般用于U盘, 相机存储, 手机存储, SSD等.

磁盘硬件构造略过. 现代操作系统隐藏了复杂性, 将磁盘抽象为一个简单的视图, 一个B个扇区大小的逻辑块, 编号为0,1,2,...,B-1. 磁盘控制器维护着逻辑块号与实际磁盘扇区的映射关系, 一个逻辑块号对应一个盘面, 磁道, 扇区的三元组.

I/O设备

连接I/O设备需要I/O总线, 如PCI(Peripheral Component Interconnect)总线. 包含如下类型:

- USB(Universal Serial Bus)通用串行总线, USB 3.0最大带宽625MB/s, USB 3.1最大带宽1250MB/s, USB 3.2最大2500MB/s, USB4最大5000MB/s.

- 显卡.

- 主机总线适配器, 用于连接磁盘. SATA只能连接一个磁盘, SCSI能连更多磁盘, 也更快更贵.

- 其他设备, 如网卡.

随着磁盘速度的提升, PCI总线逐渐满足不了需求, 催生了PCI Express(PCI-e)总线. PCI最大带宽533MB/s, PCI Express 3.0标准 X32端口支持320Gbps.

CPU使用一种称为内存映射I/O(memory-mapped I/O)的技术向I/O设备发射命令, 地址空间有一块地址是为与I/O设备通信保留的. 每个这样的地址称为I/O端口(port). 当一个设备连接到总线时, 与一个或多个端口相关联.

CPU读磁盘的过程为

- CPU发送第一条指令, 告诉磁盘发起一个读, 同时还发送了其他的参数, 例如当读完成, 是否中断CPU

- CPU第二条指令指明要读的逻辑块号

- CPU第三条指令指名存储的主存地址

- CPU发送完指令后就去做别的事情, 磁盘控制器收到CPU指令后, 讲逻辑块号翻译成一个扇区地址, 然后将内容直接传送到主存DMA(Direct Memory Access), 传送完成后, 磁盘控制器给CPU发送一个中断信号. 这会导致CPU暂停工作, 跳转到一个操作系统例程, 这个例程会记录I/O操作已完成, 然后将控制返回到CPU被中断的地方.

局部性

时间局部性, 被引用过一次的内存位置可能在不远的将来再被多次引用.

空间局部性, 如果一个内存位置被引用了一次, 那么程序很可能在不远的将来引用附件的一个内存位置.

循环时, 以步长为1的方式引用内存地址, 空间局部性是最好的.

其他

缓存不光在硬件中应用, 在软件中也大量使用了缓存的概念. 缓存的优点是加快了数据的读取速度, 弊端是可能会取到失效数据, 如何设计失效策略很重要.