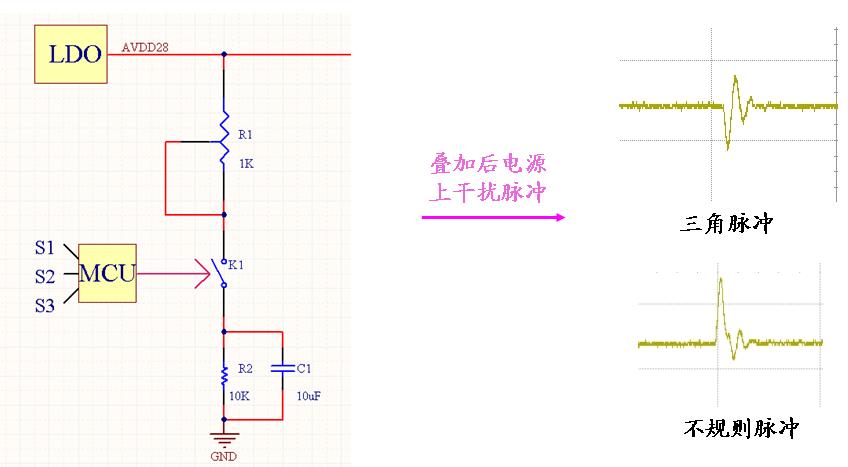

原理:通过MCU控制开关K1通断,产生尖脉冲叠加到电源上,电位器对脉冲幅度、波形进

行调节。通过按键(S1/2/3)选择输出不同频率,及占空比可调,使干扰测试更加灵活。

这里的MCU用CPLD代替,因有现成的CPLD板子,故用的Verilog写的,代码如下:

1 module Counter( 2 rst_n, 3 clk_in, 4 key_add, 5 key_sub, 6 key_mode, 7 oe, 8 clk_out 9 ); 10 input clk_in; 11 input rst_n; 12 input key_add; 13 input key_sub; 14 input key_mode; 15 output oe; 16 output clk_out; 17 18 parameter T22MS = 20'd667_999; 19 parameter T33US = 10'd999; //33us 20 parameter T11US = 9'd332; //11us 21 22 /*************************************************************/ 23 // key detect 24 reg[2:0] key_add_clk; 25 always @(posedge clk_in or negedge rst_n) 26 if(!rst_n) key_add_clk <= 3'b111; 27 else key_add_clk <= {key_mode,key_add,key_sub}; 28 29 reg[2:0] key_add_clk_r; 30 always @(posedge clk_in or negedge rst_n) 31 if(!rst_n) key_add_clk_r <= 3'b111; 32 else key_add_clk_r <= key_add_clk; 33 34 wire[2:0] key_clk_en; 35 assign key_clk_en = key_add_clk_r & (~key_add_clk); 36 37 //按键消抖 38 reg[19:0] cnt; 39 always @(posedge clk_in or negedge rst_n) 40 if(!rst_n) cnt <= 20'd0; 41 else if(key_clk_en) cnt <= 20'd0; 42 else cnt <= cnt + 1'b1; 43 44 //每隔20ms就取按键上的值 45 reg[2:0] pin_status; 46 always @(posedge clk_in or negedge rst_n) 47 if(!rst_n) pin_status <= 3'b111; 48 else if(cnt == T22MS) pin_status <= {key_mode,key_add,key_sub}; 49 50 reg[2:0] pin_status_r; 51 always @(posedge clk_in or negedge rst_n) 52 if(!rst_n) pin_status_r <= 3'b111; 53 else pin_status_r <= pin_status; 54 55 //前20MS的值与后20MS的值 56 wire[2:0] pin_status_ctrl; 57 assign pin_status_ctrl = pin_status_r & (~pin_status); 58 /*************************************************************/ 59 60 /*************************************************************/ 61 //mode selct 62 //CS = 0,regulating frequency 63 //CS = 1,regulating pulse 64 reg cs; 65 always@(posedge clk_in or negedge rst_n) 66 if(~rst_n) 67 cs <= 1'b0; 68 else if(pin_status_ctrl[2]) 69 cs <= ~cs; 70 else 71 cs <= cs; 72 /*************************************************************/ 73 74 /*************************************************************/ 75 //regulating frequency 76 reg[11:0] buff; //max = 135us 77 always@(posedge clk_in or negedge rst_n) 78 if(~rst_n) 79 buff <= T11US; 80 else if(~cs) 81 begin 82 if(pin_status_ctrl[1]) 83 begin 84 if((buff < 12'd4095)&&(buff >= T11US)) 85 begin 86 buff <= buff + 7'd100; //3us 87 if(buff >=12'd4095) 88 buff <= T11US; 89 end 90 else 91 buff <= T11US; 92 end 93 else if(pin_status_ctrl[0]) 94 begin 95 if((buff > T11US) && (buff <=12'd4095)) 96 begin 97 buff <= buff - 7'd100; 98 if(buff <= T11US) 99 buff <= 12'd4095; 100 end 101 else 102 buff <= 12'd4095; 103 end 104 end 105 106 reg[11:0] cnt1; 107 reg clk_tmp; 108 always@(posedge clk_in or negedge rst_n) 109 if(~rst_n) 110 begin 111 cnt1 <= 0; 112 clk_tmp <= 1'b0; 113 end 114 else if(~cs) 115 begin 116 if(cnt1 == buff) 117 begin 118 cnt1 <= 0; 119 clk_tmp <= ~clk_tmp; 120 end 121 else 122 cnt1 <= cnt1 + 1'b1; 123 end 124 /*************************************************************/ 125 /*************************************************************/ 126 //regulating pulse width (duty ratio) 127 reg[31:0] number; 128 always@(posedge clk_in or negedge rst_n) 129 if(~rst_n) 130 number <= buff;//32'd10; 131 else if(cs) 132 begin 133 if(number == period) 134 number<= 32'd10; 135 else if(pin_status_ctrl[1]) 136 begin 137 number <= number + 4'd10;//1'b1; 138 if(number >= period) 139 number <= 32'd10; 140 end 141 else if(pin_status_ctrl[0]) 142 begin 143 number <= number - 4'd10;//1'b1 144 if(number <= 32'd10) 145 number <= period - 1'b1; 146 end 147 else 148 number <= number; 149 end 150 else 151 number <= buff; 152 153 reg[31:0] cnt2; 154 always@(posedge clk_in or negedge rst_n) 155 if(~rst_n) 156 cnt2 <= 32'h0000_0000; 157 else if(cs) 158 begin 159 if(cnt2 == period) 160 cnt2 <= 32'h0000_0000; 161 else 162 cnt2 <= cnt2 + 1'b1; 163 end 164 else 165 cnt2 <= 32'h0000_0000; 166 167 reg pwm_tmp; 168 always@(posedge clk_in or negedge rst_n) 169 if(~rst_n) 170 pwm_tmp <= 1'b0; 171 else if(cs) 172 begin 173 case(cnt2) 174 32'd0: pwm_tmp <= 1'b1; 175 number: pwm_tmp <= 1'b0; 176 period: pwm_tmp <= 1'b1; 177 default: pwm_tmp <= pwm_tmp; 178 endcase 179 end 180 /*************************************************************/ 181 /*************************************************************/ 182 wire[31:0] period; 183 assign period = buff<<1; //period = buff x 2 184 assign oe = 1'b0; 185 assign clk_out = cs ? pwm_tmp:clk_tmp; 186 /*************************************************************/ 187 endmodule

该代码功能输出的频率可调,占空比也可调。