避免意外生成锁存器

使用always块生成组合逻辑电路时,如果变量所有可能的取值没有被考虑完全

,那么综合后可能会出现锁存器。如下面代码所示:

module latch_test

(

a,b,d,

c);

input [1:0] a,b,d;

output [1:0] c;

reg [1:0] c;

(

a,b,d,

c);

input [1:0] a,b,d;

output [1:0] c;

reg [1:0] c;

always @ (*)

begin

if(a<b)

c=d;

end

endmodule

begin

if(a<b)

c=d;

end

endmodule

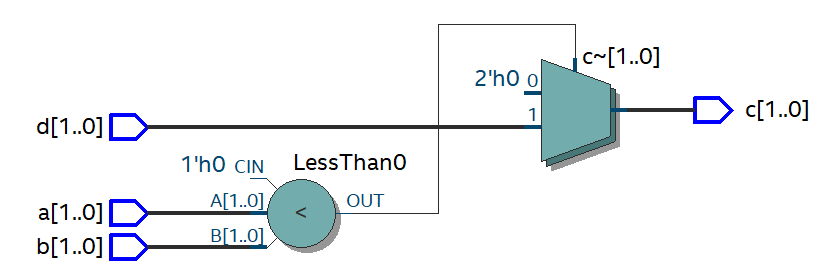

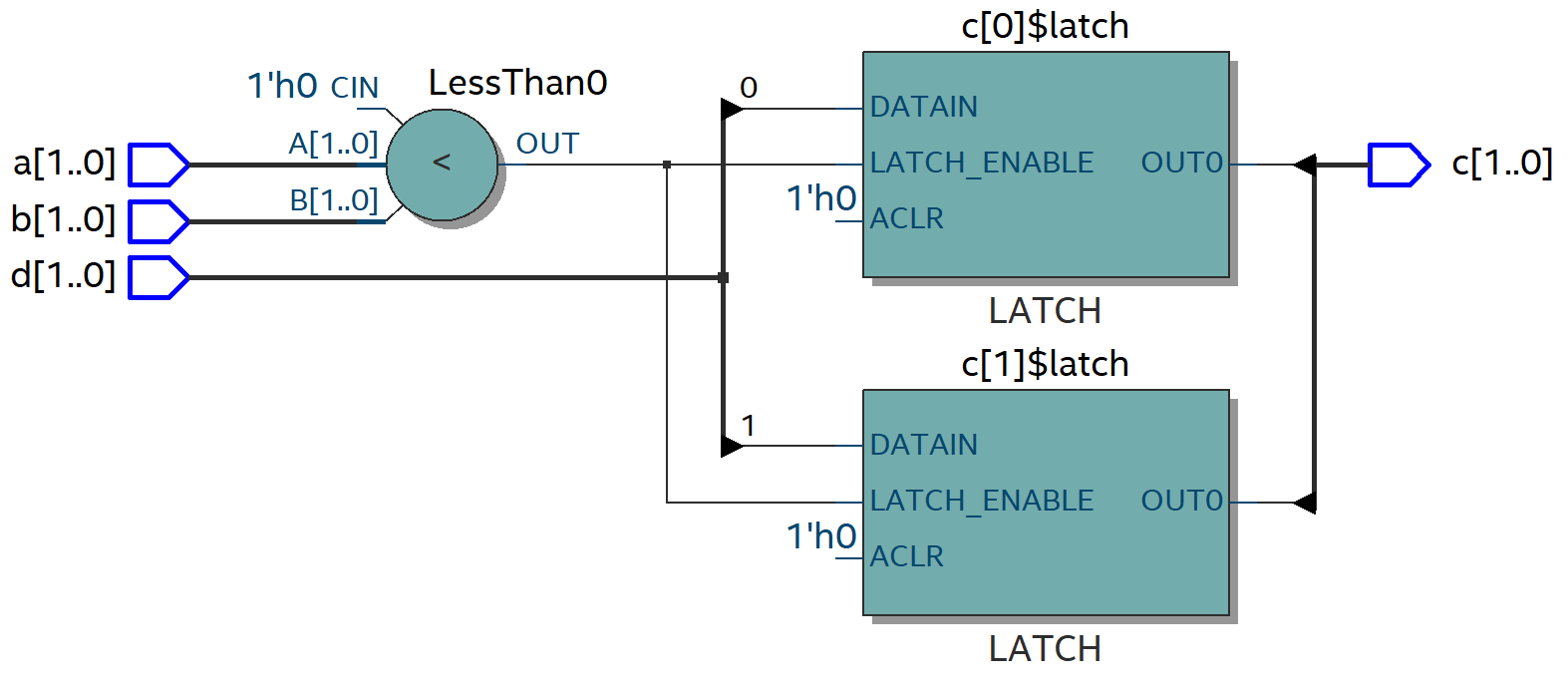

这个例子中,给出了a<b条件为真时c的取值d,没有说明a>b时c取什么值,综合工具会认为a>b时c保持原来的值不变,这样综合后电路出现锁存器。如下图所示。

避免锁存器产生方法是给变量赋初值,或者考虑所有情况。代码如下:

always @ (*)

begin

c=0;

fi(a<b)

c=d;

end