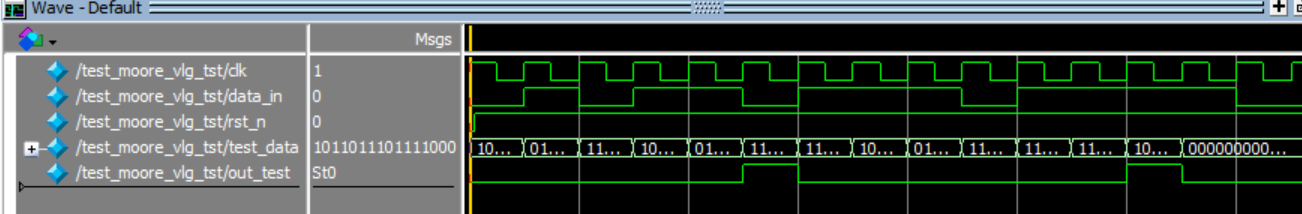

直接上RTL代码 estbench仿真图、状态图

module test_moore ( clk,rst_n,data_in,out_test ); parameter IDLE = 4'b0000, state1 = 4'b0001, state2 = 4'b0010, state3 = 4'b0100, state4 = 4'b1000; output out_test; input data_in; input clk,rst_n; reg out_test_reg; reg [3:0] state; always @ (posedge clk) begin if(!rst_n) state = IDLE; else case(state) IDLE: begin if(data_in == 1'b1) state <= state1; else state <= IDLE;end state1: begin if(data_in == 1'b0) state <= state2; else state <= state1;end state2: begin if(data_in == 1'b1) state <= state3; else state <= IDLE;end state3: begin if(data_in == 1'b1) state <= state4; else state <= state2;end state4: begin if(data_in == 1'b1) state <= IDLE; else state <= state1;end default: state <= IDLE; endcase end always @ (*) begin if(state == state4) out_test_reg = 1'b1; else out_test_reg = 1'b0; end assign out_test = out_test_reg; endmodule

//testbench `timescale 1 ps/ 1 ps module test_moore_vlg_tst(); reg clk; reg data_in; reg rst_n; reg [15:0] test_data; // wires wire out_test; test_moore i1 ( .clk(clk), .data_in(data_in), .out_test(out_test), .rst_n(rst_n) ); initial begin clk = 1'b1; rst_n = 1'b0; data_in = 1'b0; test_data = 16'b1011_0111_0111_1000; #10 rst_n = 1'b1; #100000 $stop; end always #50 clk = ~clk; always @ (posedge clk) begin if(!rst_n) data_in <= 1'b0; else begin test_data <= test_data<<1; data_in <= test_data[15]; end end endmodule