1 module sort3 2 ( 3 data_in1,data_in2,data_in3, 4 data_out1,data_out2,data_out3, 5 clk,reset 6 ); 7 8 output [7:0] data_out1,data_out2,data_out3; 9 input [7:0] data_in1,data_in2,data_in3; 10 input clk,reset; 11 12 reg [7:0] data_out1,data_out2,data_out3; 13 reg [7:0] data_tempt1,data_tempt2,data_tempt3; 14 15 always @ (posedge clk) 16 if(!reset) 17 begin 18 data_out1 <= 1'b0; 19 data_out2 <= 1'b0; 20 data_out3 <= 1'b0; 21 end 22 else 23 begin 24 {data_tempt1,data_tempt2,data_tempt3}={data_in1,data_in2,data_in3}; 25 sort2(data_tempt1,data_tempt2); 26 sort2(data_tempt1,data_tempt3); 27 sort2(data_tempt2,data_tempt3); 28 {data_out1,data_out2,data_out3}={data_tempt1,data_tempt2,data_tempt3}; 29 end 30 31 task sort2; 32 inout [7:0] x,y; 33 reg [7:0] temp; 34 if(x > y) 35 begin 36 temp = x; 37 x = y; //因为需要做数据交换,所以用blocking赋值 38 y = temp; 39 end 40 endtask 41 42 endmodule

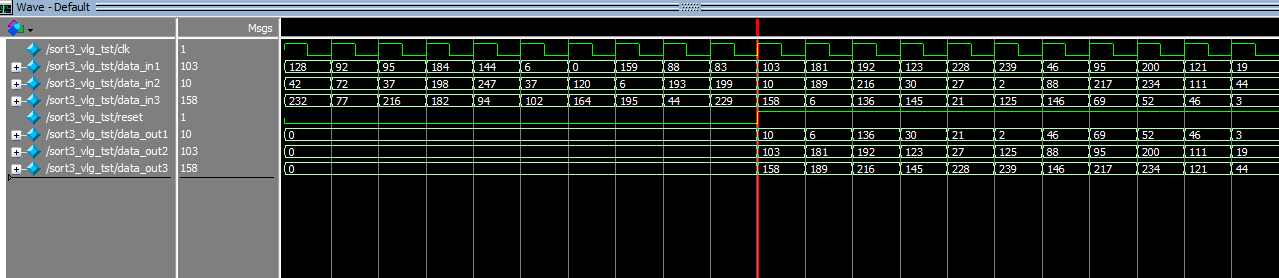

数字排序,用到了blocking,仿真结果正确。

1 module sort3 2 ( 3 data_in1,data_in2,data_in3, 4 data_out1,data_out2,data_out3, 5 clk,reset 6 ); 7 8 output [7:0] data_out1,data_out2,data_out3; 9 input [7:0] data_in1,data_in2,data_in3; 10 input clk,reset; 11 12 reg [7:0] data_out1,data_out2,data_out3;13 reg [7:0] data_tempt1,data_tempt2,data_tempt3; 14 15 always @ (posedge clk) 16 if(!reset) 17 begin 18 data_out1 <= 1'b0; 19 data_out2 <= 1'b0; 20 data_out3 <= 1'b0; 21 end 22 else 23 begin 24 {data_tempt1,data_tempt2,data_tempt3}={data_in1,data_in2,data_in3}; 25 sort2(data_tempt1,data_tempt2); 26 sort2(data_tempt1,data_tempt3); 27 sort2(data_tempt2,data_tempt3); 28 {data_out1,data_out2,data_out3}={data_tempt1,data_tempt2,data_tempt3}; 29 end 30 31 task sort2; 32 inout [7:0] x,y; 33 reg [7:0] temp; 34 if(x > y) 35 begin 36 temp <= x; 37 x <= y; //因为需要做数据交换,所以用blocking赋值 38 y <= temp; 39 end 40 endtask 41 42 endmodule

nonblocking仿真结果错误。

在编写时牢记这八个要点可以为绝大多数的

Verilog 用户解决在综合后仿真中出现的 90-100% 的冒险竞争问题。

1) 时序电路建模时,用非阻塞赋值。

2) 锁存器电路建模时,用非阻塞赋值。

3) 用 always 块建立组合逻辑模型时,用阻塞赋值。

4) 在同一个 always 块中建立时序和组合逻辑电路时,用非阻塞赋值。

5) 在同一个 always 块中不要既用非阻塞赋值又用阻塞赋值。

6) 不要在一个以上的 always 块中为同一个变量赋值。

7) 用$strobe 系统任务来显示用非阻塞赋值的变量值

8) 在赋值时不要使用 #0 延迟