2017-2018-1 20155324 《信息安全系统设计基础》第七周学习总结

教材学习内容总结

ISA的定义

指令集体系结构(ISA)定义了处理器状态、指令的格式、以及每条指令对状态的影响。大多数ISA包括IA32和x84-64,将程序的行为描述成好像每条指令是按顺序执行的。

指令集体系统:一个处理器支持的指令和指令的字节级编码,每种不同的处理器都有自己不同的ISA

Y86指令集体系结构

定义一个指令集体系结构,包括定义各种状态元素,指令集和他们的编码、一组程序规范和异常处理。

-

RF程序寄存器:%eax,%ecx,%edx,%ebx,%esi,%edi,%esp,%ebp(%esp被入栈、出栈、调用和返回指令作为栈指针)

-

PC程序计数器:存放当前正在执行指令的地址

-

DEME存储器:一个很大的字节数组,保存着程序和数据

-

Stat程序状态:表明程序执行的总体状态

-

CC条件码:ZF、SF、OF

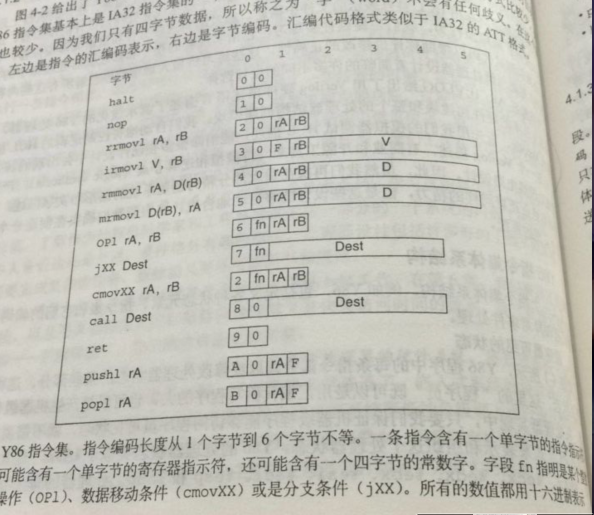

·Y86 ISA中各指令

-

IA32的movl指令分为4个不同的指令:irmovl,rrmovl,mrmovl和rmmovl

-

有4个整数操作指令:addl,subl,andl和xorl

-

7个跳转码:jmp,jle,ji,je,jne,jge和jg

-

6个条件传送码:cmovle,cmovl,cmove,cmovne,cmovge和cmovg

-

call:将返回地址入栈,然后跳到目的地址。 ret:从这样的过程调用中返回。

-

pushl和popl:入栈和出栈

-

halt:停止指令的执行

状态码Stat:

-

值1 AOK 正常操作

-

值2 HLT 处理器执行halt指令

-

值3 ADR 遇到非法地址

-

值4 INS 遇到非法指令

逻辑设计和硬件控制语言HCL

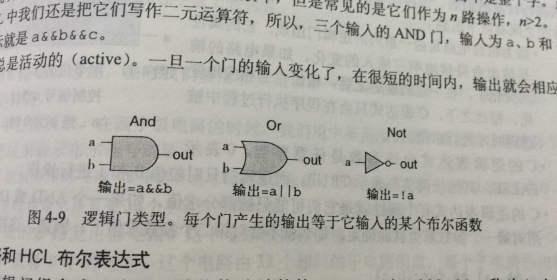

逻辑门:AND => && Or => || Not => !

组合电路和HCL布尔表达式:很多逻辑门组成一个网。逻辑门的输出不能连接在一起。必须无环。多路复用器:根据输入控制信号的值,从一组不同的数据信号中选出一个。

存储器和时钟:为了产生时序电路,也就是有状态并且在这个状态上进行计算的系统,我们必须引入安位存储信息的设备,存储设备都是有同一个时钟控制,时钟是一个周期性信号。

组合电路和HCL布尔表达式

组合电路:将很多逻辑门组成一个网

- 两条限制:

1.两个或多个逻辑门的输出不能连接在一起。

2.这个网必须是无环的

存储器和周期:

时钟寄存器:简称寄存器。存储单个位或字。时钟信号控制寄存器加载输入值

随机访问存储器:简称存储器。存储多个字,用地址来选择该读或该写哪个字。

寄存器文件有两个读端口(A和B),还有一个写端口W。这样一个多端口随机访问存储器允许同时进行多个读和写的操作。每个端口都有一个地址输入,表明该选择哪个程序寄存器。

Y86异常

状态码:描述程序执行的总体状态。

| 值 | 名字 | 含义 |

|---|---|---|

| 1 | AOK | 正常操作 |

| 2 | HLT | 处理器执行halt指令(指令停止) |

| 3 | ADR | 遇到非法地址 |

| 4 | INS | 遇到非法指令 |

Y86中,任何AOK以外的代码都会使处理器停止执行指令,而没有异常处理程序。

HCL中,所有字级的信号都声明为int,不指定字的大小

下面是两个汇编完的Y86指令以及对应的机器编码:

教材学习中的问题和解决过程

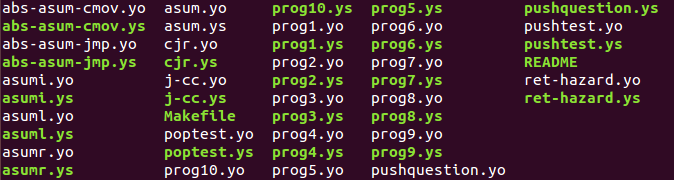

ys是源代码 .yo是汇编后的结果,用make指令可以进行汇编

代码托管

尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。

耗时估计的公式

:Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。

-

计划学习时间:XX小时

-

实际学习时间:XX小时

-

改进情况:

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)