一、DRAM的存储元电路

常见的DRAM存储元电路有四管式和单管式两种,它们的共同特点是靠电容存储电荷的原理来存储信息。电容上存有足够多的电荷表示“1”,电容上无电荷表示“0”。 由于电容存储的电荷会逐渐泄漏,即使电源不掉电,信息也会很快消失,应用中需要定时恢复存储的电荷。与SRAM相比,DRAM具有集成度高,功耗低等特点,目前被广泛应用于各类计算机中。

四管DRAM存储元

二、

刷新操作:由于存储的信息电荷终究是有泄漏的,时间久了,信息就会丢失。为此,必须设法由外界按一定规律不断给栅极进行充电,补足栅极的信息电荷,这就是所谓“再生”或“刷新”。

设原存信息为“1”,T1管截止,T2管导通。若经过一段时间,T2管栅极上漏失一部分信息电荷,使A端的电压稍小于存“1”时的满值电压。此时,在字选择线上加脉冲,T5、T6开启,A端与位线D相连,从而充电到满值电压,刷新了原存“1”的信息。因此,定时给全部存储单元电路执行一遍读操作,就可以实现信息再生。

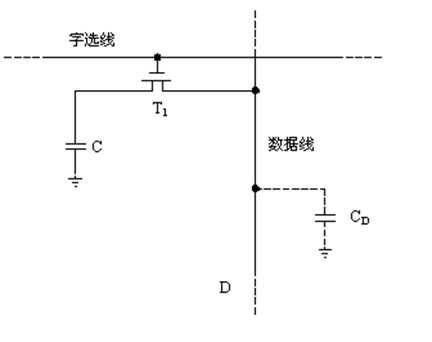

三、单管DRAM存储元

为提高芯片的存储密度,现在动态RAM芯片中一般采用图4-9所示的单管动态存储元电路,其中T1管为字选控制管,字选线有效(高电位)使其导通。

读操作:字选择线为“1”,使T1管导通。若原存“1”,则C上电荷通过T1管向位线(数据线)泄放,通过读出放大器形成读“1”信号。反之,若原存“0”,则无泄放电流。因为读出时C电荷泄放,电位下降,所以是破坏性读出,在读出后应有重写操作。

写操作:字选择线为“1”,使T1管导通。要写“1”,在位线(数据线)上加高电位,经T1管对C充电;写“0”则在数据线上加低电位,使CD上无电荷。

刷新操作:由于MOS管栅极电容上存储的电荷会缓慢泄放,超过一定时间(2~3.3ms),就会丢失信息。因此必须定时给栅级电容补充电荷,进行“刷新”操作。

单管DRAM存储元电路

四、DRAM存储器芯片的读/写周期

读周期

DRAM的读周期时序如图4-11(a)所示。

为了使芯片能正确地接收行、列地址并实现读操作,各信号的时间关系应符合下面的要求:行地址必须在RAS#信号有效之前送到芯片的地址输入端;CAS#信号应滞后RAS#一段时间,并滞后于列地址送到芯片地址输入端的时间;RAS#、CAS#应有足够的宽度;WE#信号为高,并在CAS#有效之前建立。

图为DRAM时序

写周期

DRAM的写周期时序如图4-11(b)所示。

有两点需要说明一下:

1、WE#信号为低,并在信号CAS#有效之前建立。

2、数据必须在CAS#有效之前出现在DIN端。

五、DRAM的刷新

刷新的实质是先将原存信息读出,再由刷新放大器形成原信息并重新写入的再生过程。由于存储元被访问是随机的,有可能某些存储元长期得不到访问,无读出也就无重写,其原信息必然消失。为此,必须采用定时刷新的方法,规定在一定的时间内,对DRAM的全部存储元电路做一次刷新,这一段时间间隔叫做刷新周期,或叫再生周期,一般取2ms、4ms或8ms。