一、MIPI

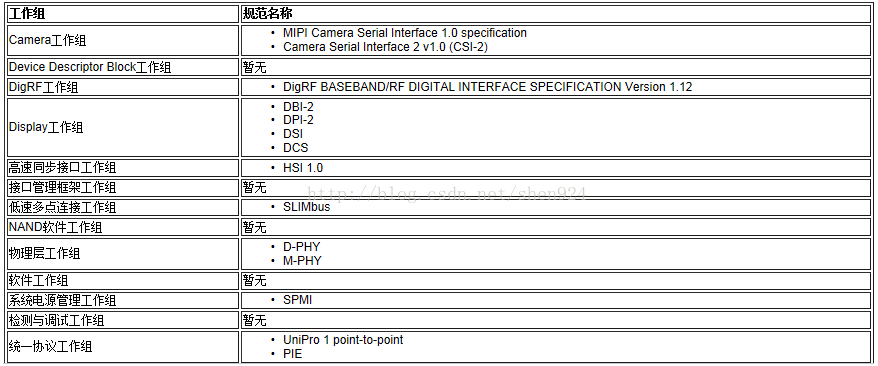

MIPI(Mobile Industry Processor Interface/移动工业处理器接口)是2003年由ARM、Nokia、ST 等公司成立联盟并为移动应用处理器制定的一个开放标准, 旨在将各个模块标准化以降低设计的复杂度和兼容性。 由于定义的范围太广,所以在针对具体的模块有自己一套协议,已经完成和正在计划中的规范如下:

本文主要介绍用于显示的协议 -- MIPI DSI, 以及同样用于显示的DBI/DPI各自的差异和特点。

=============================== 以下分析以ST7789V芯片为例 =================================================

二、DBI

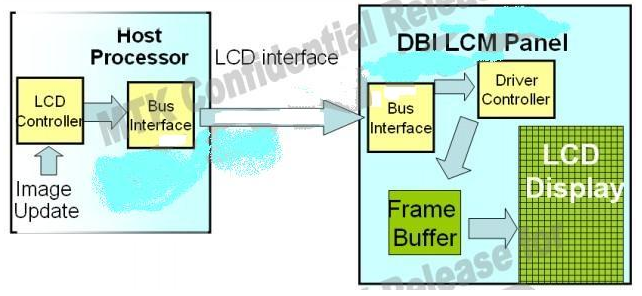

DBI(Display Bus Interface), 显示总线接口, 也称MCU接口或者80/8080接口, 整个框架如下:

DBI接口最大的特点就是LCM自带framebuffer, 存储Host端发过来的数据, 并由内部的控制IC不断重复的刷到LCD上, 也就是说其内部实现了自刷新, Host只要发送一次数据即可, 这帧数据会一直显示在屏幕上。

由于不需要Host端自刷新,对Host处理器的要求很低, 没有时钟线,Host和LCM可以是简单的GPIO相连, 这也是叫MCU接口的原因, 典型的可以和51单片机相连, 只要满足时序要求即可。

ST7789V芯片支持DBI接口, 根据数据传输又可分为并口和串口传输(主要体现在数据线上,其他时序要求都是一样的)

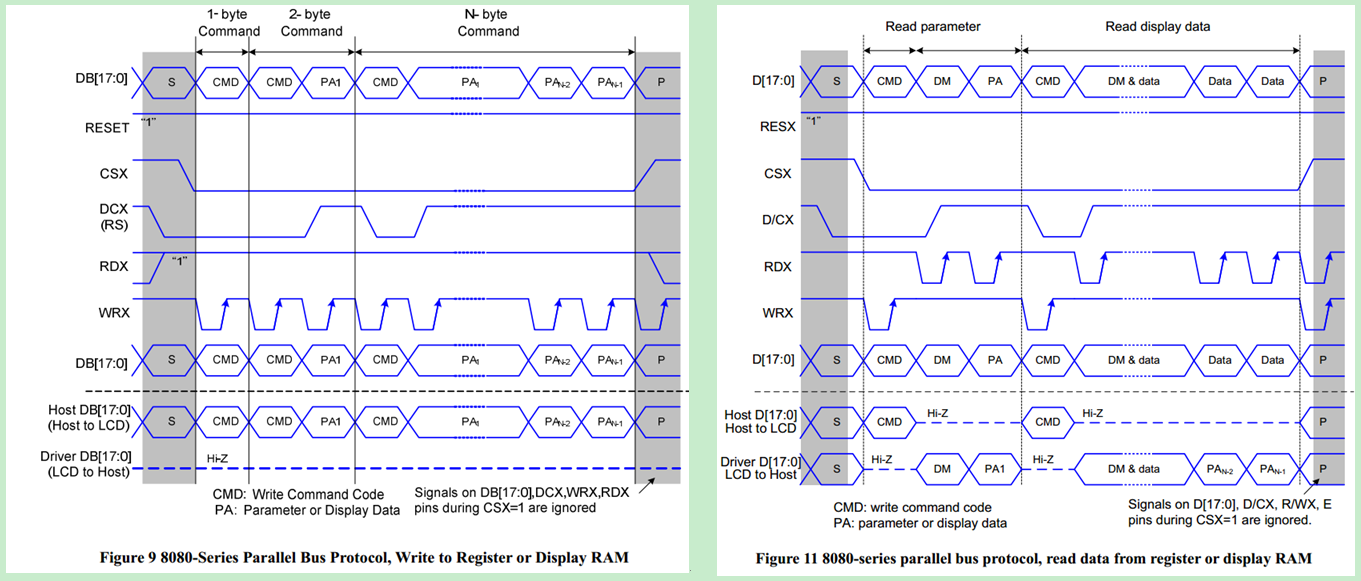

1. 并口传输:

CSX: 片选信号,图中低电平有效; D/CX:数据/命令信号; WRX: 写使能, 上升沿锁存; RDX:读使能, 上升沿锁存; D[17:0]: 数据, 具体使用多少根数据线可配置

根据M0~3四根引脚配置有如下:

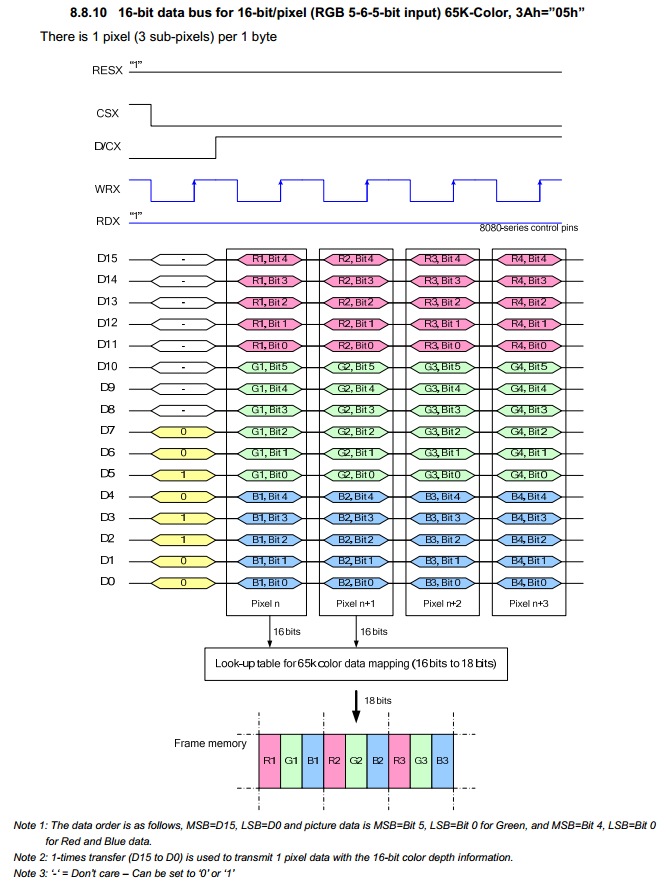

已0001为例, 数据使用16根线D[15:0](针对RGB565格式),可以看出当D/CX=0,RDX=1, WRX上升沿时为写命令, 有效长度为一个byte位于D[7:0], 而D/CX=1是写数据, 根据前面的命令决定后面数据长度, 如果是帧数据就占16根, 如果是配置参数也是一个byte, 以此类推!

具体的写、读操作时序如下:

以RGB565刚好在D[15:0]的实际分布如下((2Ch): Memory Write, 写命令0x2c, 接着开始写帧数据 ):

除了上述GPIO引脚外, 一般还有TE(tearing effect)引脚, Host可以通过该引脚得知LCM一帧数据是否刷完(也可配置LCM每刷多少帧产生一个信号告知Host), 以做同步。

2. 串口传输

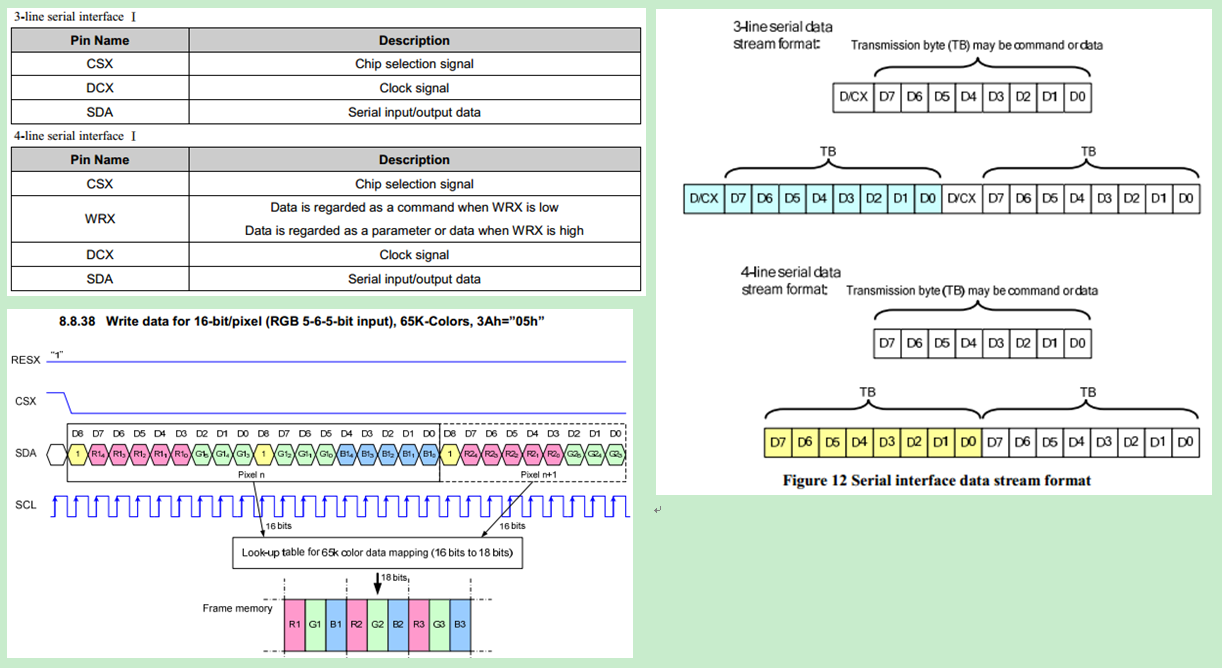

ST7789V串口传输有3线制和4线制, 主要区别在于识别数据线的数据是显示数据还是命令, 如下:

3线制每传输一个字节需要9bit, 多出一个bit来表示该字节是命令还是数据, 4线制每byte就是8bit,通过这根多出的引脚告知LCM这个byte是命令还是数据。

注意: 如果3线制采用MCU GPIO实现将非常简单, 如果采用SPI传输就会有个问题, SPI主控器一般发送单位是8bit, 无法生成图上每9bit构成一个字节, 设置在SPI传输时是可以设置的 “spi->bits_per_word = 9;”也不行, 因为在SPI主控器

会设置成两个字节为单位进行传输, 可以理解为short类型, 举个例子: 假设现在传输4个字节,可以设置“spi->len = 4;” “spi->bits_per_word = 8;” CPU 会从内存读取4次丢到SPI寄存器 readb()/writeb(), 如果 “spi->bits_per_word = 9;”

SPI主控器会设置步进2byte, CPU从内存读取两次每次两个字节丢到SPI寄存器, 当然最后在线上的波形都是4个字节, 不同的是: a. 时序可能不同, CPU大端 两次char丢和一次short丢位置是相反的!; b. short只丢两次效率更高

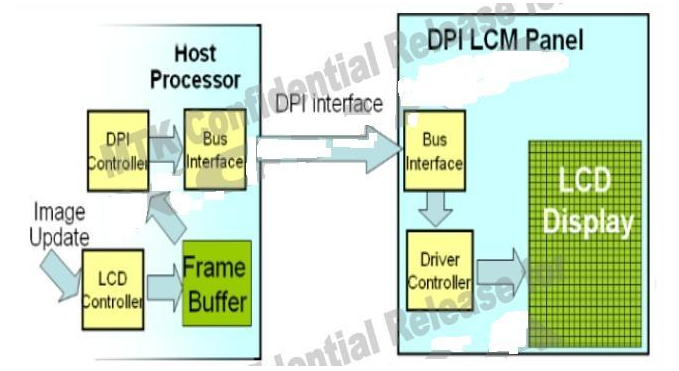

三、DPI

DPI(Display Pixel Interface) 显示像素接口, 也称RGB接口, 之所以叫像素接口, 是因为数据采用并口在一个时钟周期就传输一个像素的数据, 所以时钟一般设置像素时钟而不是bit时钟, 整个框架如下:

与DBI不同的是, LCM端没有framebuffer, 转移到Host端, 所以为了维持画面能够持续显示在屏幕上, Host要持续发送数据过去, 并且为保证数据的同步, 引入VSYNC/HSYNC等功能(更准确说是继承了以前的叫法), 如下:

解释如下:

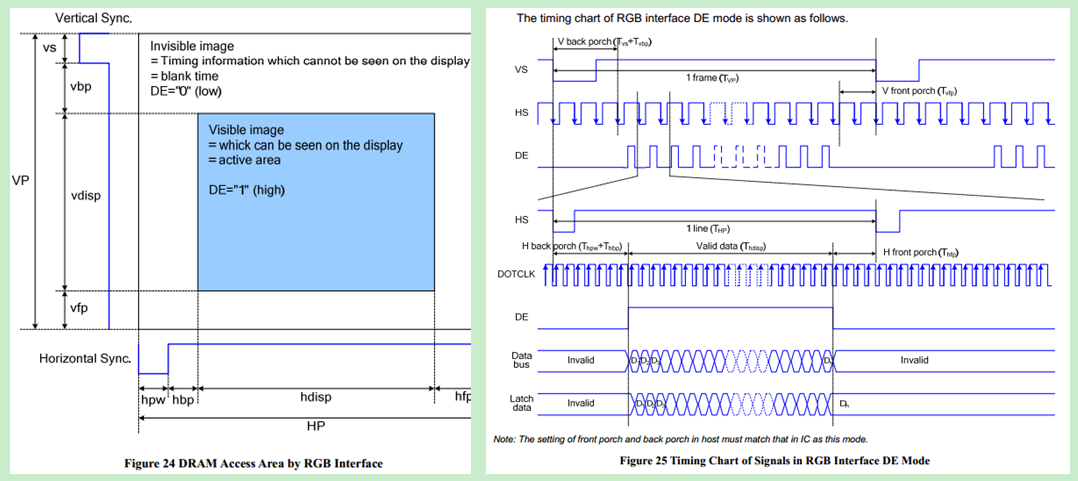

Vsync:帧同步信号, 告知LCM移到帧起始位置,从上图Figure25可以知道水平就是低电平有效(不是高电平), 极性就是下降沿有效(看一个周期的开始)

vbp: 帧同步信号的后肩(在Vsyc后面),单位为1行的时间。

vfp: 帧同步信号的前肩(在Vsyc前面),单位为1行的时间。

Hsync:行同步信号, 告知LCM移到下一行的起始位置, 从上图Figure25可以知道水平就是低电平有效(不是高电平), 极性就是下降沿有效(看一个周期的开始)

hbp:行同步信号的后肩(在Hsyc后面),单位为1像素的时间。

hfp:行同步信号的前肩(在Hsyc前面),单位为1像素的时间。

Dotclk:点时钟或称像素时钟

DE: 数据有效信号(重点,后面会详解)

对于DBI接口, 每次发送帧数据时会先发送个命令(上文提到0x2c), 而RGB接口不同发送命令, 可通过Vsync、Hsync告知LCM接收新一帧数据。那vbp/vfp/hbp/hfp又是干嘛的呢? 对于我们这种TFT屏来说可以不用, 主要是兼容早期的显示屏:

以前显示技术是CRT(阴极射线显像管), 尾部是电子枪, 靠电子撞击玻璃产生亮度(所以只有黑白两种颜色), 由于电子枪扫射是机械行为, 所以当换行尤其是最后一行最后一个像素点要移到第一行第一个像素换帧的时候, 机械运动需要时间, 因此

要加延迟操作,这期间时钟还是一直在跑, 使得主控和显示模块保持同步, 当电池抢移到位置且稳定时, 主控器就可以读取数据并传输到数据线就上, 问题是显示模块如何知道此时数据线上的数据是有效数据了? 就是DE线告知的, 这个是主控器

“自动”操作DE线的, 其时机就是根据vbp/vfp/hbp/hfp参数控制的,当Vsync/Hsync有效后, 主控器并不会立即读取帧数据放到数据线, 而是disable DE, 让显示模块ready, 然后经过Vsync/vbp/vfp/后开始读取帧数据并使能DE引脚, 这时显示模块

就接收帧数据了! 而TFT屏本可以不用这四个参数, V/Hsync有效后直接发送帧数据, 但为了兼容CRT所以还是保留下来了, 其实除了这四个参数, 连V/Hsync都可以不要, 因为DPI的数据线只是传输帧数据, 初始化参数命令还是要通过其他比如SPI发送的

那这个同步信号完全可以通过SPI发送过去, 然后帧数据就发送到数据线(即除了上面的Dotclk,其余都可以不用), 当然目前还是继承并使用这些参数, 所以一个典型的BPI接口电路如下:

没错, 最大的缺点就是 浪费线! 控制部分一般是SPI接口, 数据部分就是一堆的RGB线, 那相比DBI 中3线制有什么优势呢? 没错, 就是传输快! 尤其V/Hsync代替发送帧同步命令, 可以无间隔存粹传输帧数据! 一般用于屏幕大(像素高)的LCM产品。

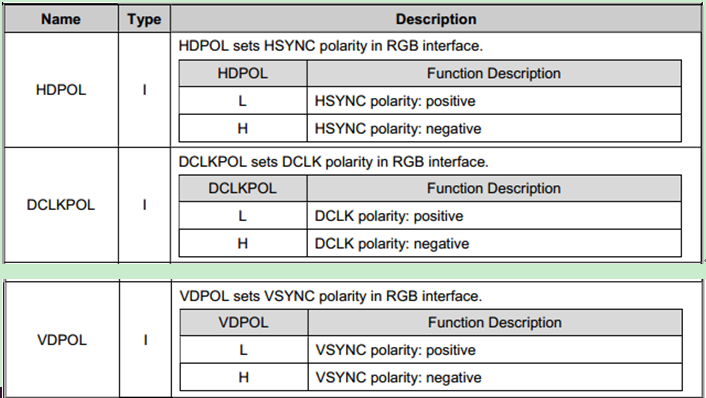

还有关于极性的设置, V/Hsync、Dotclk和DE都可以可以设置的, 以ST7789V为例:

如果LCM实际时序跟Figure25一致的话, 可以反推LCM硬件电路设置VSPL/HSPL 接VCC, DPL/EPL接地

注意: 这些极性是由LCM设定的(不是显示芯片, 它只是提供这个能力, 取决模组厂家硬件电路设置), Host要根据其要求设置极性, 比如我现在调试某家LCM模组厂家, 显示芯片采用ST7272A, 其手册极性描述如下:

从LCM厂家给的原理图,这四个引脚模组厂直接接VCC,

可以知道其波形为下图红色圈圈, 也就是极性为下降沿有效, 电平是高电平有效:

而我的主控器是博通5892, 设置极性是电平不是极性, 也即设置低电平有效(=1):

四、DSI

DSI(Display Serial Interface) 显示串行接口, 帧数据/命令全使用串口方式传输(打成一个包), 1~4通道, 由于篇幅问题, 在下一篇博文再详细介绍。