以太网PHY和MAC之间一般有如下接口,具体的接口描述可以在PHY芯片数据手册查看到:

MII:参考:DP83640 Precision PHYTER™ - IEEE 1588 Precision Time Protocol Transceiver

MDIO接口时序:

RMII:

GMII:88E1119R

############################################################

# RX Clock period Constraints (per instance) #

############################################################

# Receiver clock period constraints: please do not relax

set rx_clk [get_clocks -of [get_ports gmii_rx_clk]]

############################################################

# Obtain input clocks from top level XDC #

############################################################

set ip_gtx_clk [get_clocks -of_objects [get_ports gtx_clk]]

set ip_mii_tx_clk [get_clocks -of_objects [get_ports mii_tx_clk]]

############################################################

# Define clock relationships #

############################################################

set_clock_groups -logically_exclusive -group $ip_gtx_clk -group $ip_mii_tx_clk

#

####

#######

##########

#############

#################

#BLOCK CONSTRAINTS

############################################################

# For Setup and Hold time analysis on GMII #

############################################################

# Identify GMII Rx Pads only.

# This prevents setup/hold analysis being performed on false inputs,

# eg, the configuration_vector inputs.

# The following constraints work in conjunction with IDELAY_VALUE settings to

# check that the GMII receive bus remains in alignment with the rising edge of

# GMII_RX_CLK.

set_input_delay -clock $rx_clk -max 6 [get_ports {gmii_rxd[*] gmii_rx_er gmii_rx_dv}]

set_input_delay -clock $rx_clk -min 0.6 -add_delay [get_ports {gmii_rxd[*] gmii_rx_er gmii_rx_dv}]

# Need to force the ignore inputs as these currently prevent clock propogation through the BUFGMUX

set_case_analysis 0 [get_pins tri_mode_ethernet_mac_i/clock_inst/BUFGMUX_SPEED_CLK/IGNORE*]

# create a generated clock to allow the GMII tx to be timed

create_generated_clock -name [current_instance .]_gmii_ext_clk -divide_by 1 -invert -source [get_pins {tri_mode_ethernet_mac_i/gmii_interface/gmii_tx_clk_ddr_iob/C}] [get_ports gmii_tx_clk] -add -master_clock $ip_gtx_clk

set gmii_ext_clk [current_instance .]_gmii_ext_clk

# the output delays are analysed with respect to the generated clock

set_output_delay 2 -max -clock [get_clocks $gmii_ext_clk] [get_ports {gmii_txd[*] gmii_tx_er gmii_tx_en}]

set_output_delay -1.8 -min -clock [get_clocks $gmii_ext_clk] [get_ports {gmii_txd[*] gmii_tx_er gmii_tx_en}]

# remove paths from mii_tx_clk to the new clock as we do not want to time them with these constraints

set_false_path -from $ip_mii_tx_clk -to [get_clocks $gmii_ext_clk]

############################################################

# Crossing of Clock Domain Constraints: please do not edit #

############################################################

# set a false path for the IPIF

set_max_delay -from [get_cells {tri_mode_ethernet_mac_i/axi4_lite_ipif/axi4_lite_ipif_top_wrapper/axi_lite_top/*/bus2ip_addr_i_reg[*]}] -to $ip_gtx_clk 6 -datapath_only

# set a false path for the IPIF

set_max_delay -from [get_cells {tri_mode_ethernet_mac_i/axi4_lite_ipif/axi4_lite_ipif_top_wrapper/axi_lite_top/*/bus2ip_addr_i_reg[*]}] -to $ip_mii_tx_clk 6 -datapath_only

# set a false path for the static config registers

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg[*]}] -to $ip_gtx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg[*]}] -to $ip_mii_tx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg[*]}] -to $rx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg}] -to $ip_gtx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg}] -to $ip_mii_tx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg}] -to $rx_clk

RGMII:88E1116R

注意RGMII的时序有两种,可以选择配置PHY端加延时或MAC端加延时

############################################################

# RX Clock period Constraints (per instance) #

############################################################

# Receiver clock period constraints: please do not relax

set rx_clk [get_clocks -of [get_ports rgmii_rxc]]

############################################################

# Obtain input clocks from top level XDC #

############################################################

set ip_gtx_clk [get_clocks -of_objects [get_ports gtx_clk]]

#

####

#######

##########

#############

#################

#BLOCK CONSTRAINTS

############################################################

# For Setup and Hold time analysis on RGMII inputs #

############################################################

# define a virtual clock to simplify the timing constraints

create_clock -name [current_instance .]_rgmii_rx_clk -period 8

set rgmii_rx_clk [current_instance .]_rgmii_rx_clk

# Identify RGMII Rx Pads only.

# This prevents setup/hold analysis being performed on false inputs,

# eg, the configuration_vector inputs.

set_input_delay -clock [get_clocks $rgmii_rx_clk] -max -1 [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_input_delay -clock [get_clocks $rgmii_rx_clk] -min -2.5 [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_input_delay -clock [get_clocks $rgmii_rx_clk] -clock_fall -max -1 -add_delay [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_input_delay -clock [get_clocks $rgmii_rx_clk] -clock_fall -min -2.5 -add_delay [get_ports {rgmii_rxd[*] rgmii_rx_ctl}]

set_false_path -rise_from [get_clocks $rgmii_rx_clk] -fall_to $rx_clk -setup

set_false_path -fall_from [get_clocks $rgmii_rx_clk] -rise_to $rx_clk -setup

set_false_path -rise_from [get_clocks $rgmii_rx_clk] -rise_to $rx_clk -hold

set_false_path -fall_from [get_clocks $rgmii_rx_clk] -fall_to $rx_clk -hold

set_multicycle_path -from [get_clocks $rgmii_rx_clk] -to $rx_clk -setup 0

set_multicycle_path -from [get_clocks $rgmii_rx_clk] -to $rx_clk -hold -1

############################################################

# For Setup and Hold time analysis on RGMII outputs #

############################################################

create_generated_clock -name [current_instance .]_rgmii_tx_clk -divide_by 1 -source [get_pins {tri_mode_ethernet_mac_i/rgmii_interface/rgmii_txc_ddr/C}] [get_ports rgmii_txc]

set rgmii_tx_clk [current_instance .]_rgmii_tx_clk

set_output_delay 0.55 -max -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}]

set_output_delay -0.7 -min -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}]

set_output_delay 0.55 -max -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}] -clock_fall -add_delay

set_output_delay -0.7 -min -clock [get_clocks $rgmii_tx_clk] [get_ports {rgmii_txd[*] rgmii_tx_ctl}] -clock_fall -add_delay

set_false_path -rise_from $ip_gtx_clk -fall_to [get_clocks $rgmii_tx_clk] -setup

set_false_path -fall_from $ip_gtx_clk -rise_to [get_clocks $rgmii_tx_clk] -setup

set_false_path -rise_from $ip_gtx_clk -rise_to [get_clocks $rgmii_tx_clk] -hold

set_false_path -fall_from $ip_gtx_clk -fall_to [get_clocks $rgmii_tx_clk] -hold

set_multicycle_path -from $ip_gtx_clk -to [get_clocks $rgmii_tx_clk] 0 -setup

set_multicycle_path -from $ip_gtx_clk -to [get_clocks $rgmii_tx_clk] -1 -hold

############################################################

# Crossing of Clock Domain Constraints: please do not edit #

############################################################

# CDC from the Rx statistics to the statistic counter logic

set_max_delay -from $rx_clk -to [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*statistics_counters/general_statisic_control[*].general_statisics/sync_inc_vector/data_sync_reg0}] 6 -datapath_only

set_max_delay -from $rx_clk -to [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*statistics_counters/frame_size_bin_control1[*].frame_size_stats1/sync_inc_vector/data_sync_reg0}] 6 -datapath_only

set_max_delay -from $rx_clk -to [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*statistics_counters/frame_size_bin_control2[*].frame_size_stats2/sync_inc_vector/data_sync_reg0}] 6 -datapath_only

set_max_delay -from $rx_clk -to [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*statistics_counters/*/accum_gray_resync[*].sync_accum_gray_i/data_sync_reg0}] 6 -datapath_only

# set a false path for the IPIF

set_max_delay -from [get_cells {tri_mode_ethernet_mac_i/axi4_lite_ipif/axi4_lite_ipif_top_wrapper/axi_lite_top/*/bus2ip_addr_i_reg[*]}] -to $ip_gtx_clk 6 -datapath_only

# set a false path for the static config registers

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg[*]}] -to $ip_gtx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg[*]}] -to $rx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg}] -to $ip_gtx_clk

set_false_path -from [get_cells {tri_mode_ethernet_mac_i/bd_71fb_mac_0_core/*managen/conf/int_*reg}] -to $rx_clk

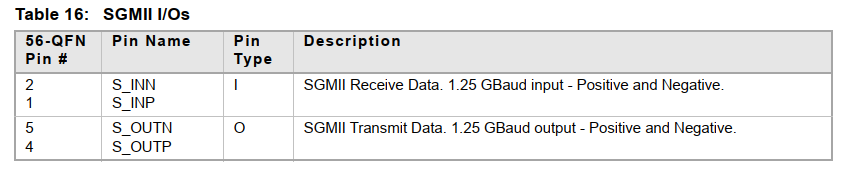

SGMII:注意,需要交换连接tx和rx