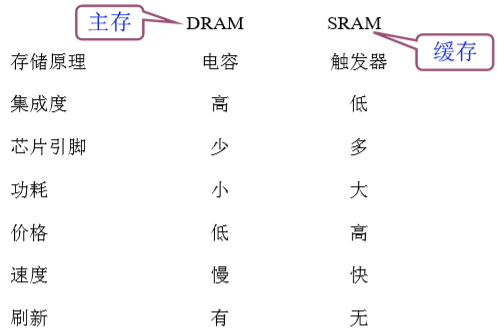

PART 2-主存储器

2.3 随机存取存储器

## 有一点点上一节的补充,我懒得换来换去了,然后就是这样了。。

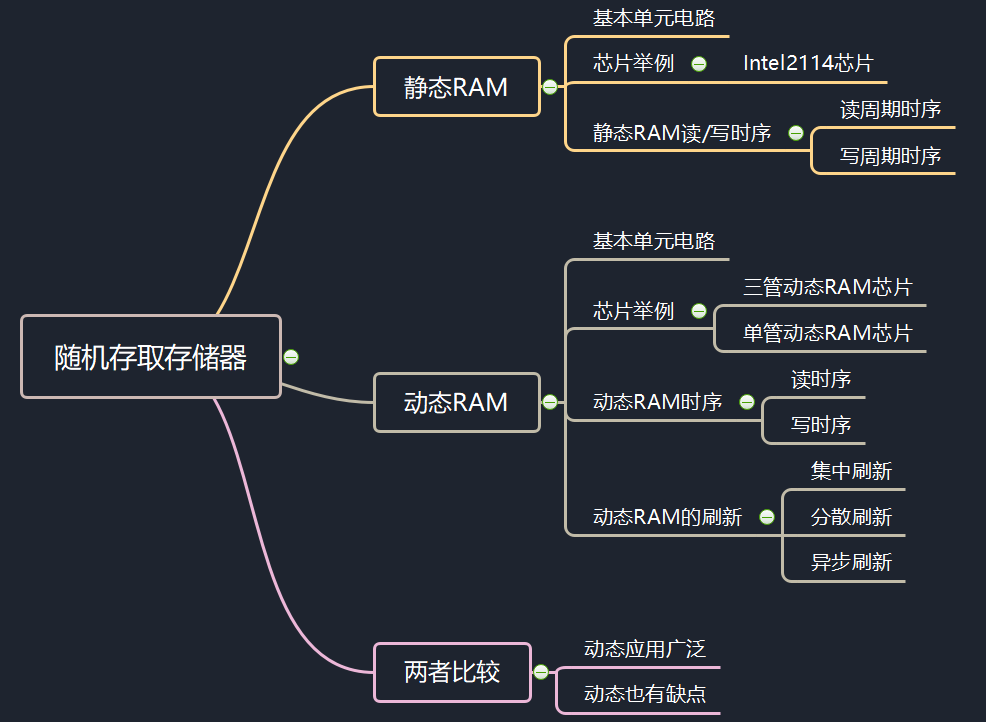

## 按存储信息的原理不同,分为静态RAM和动态ROM两大类

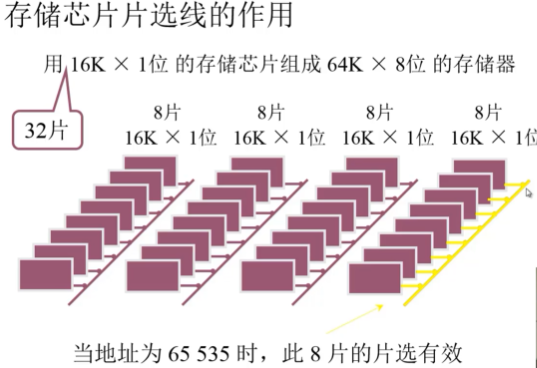

8个芯片同时工作,这样才能满足一次8位,所以八个一组,一共4组

分配地址:

第一组:0—16K-1(16384-1B)

第二组:16K—32K-1

第三组:32K—48K-1

第四组:48K—64K-1

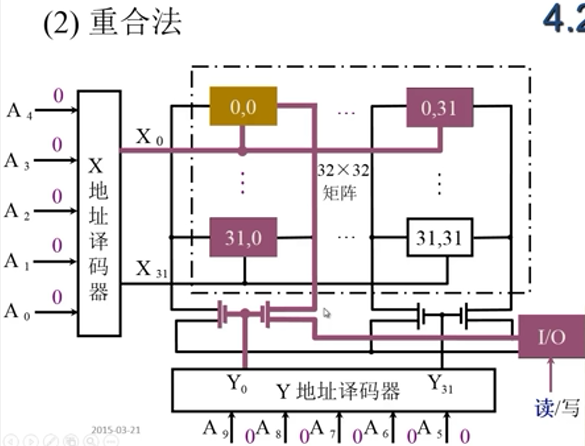

## A0~A3一共四位地址,有16个存储单元,每个存储单元多少位呢,看数据线---8位

##译码器:数电学过的,咳咳咳,我没忘。。比如说2-4译码器,输入01,则输出的四根线中,对应为1有效,其他无效;输入11,则输出为3,之类的,所以4个可以得到16个

但如果有很多线的话,就会很麻烦,很乱,毕竟几百万根呢

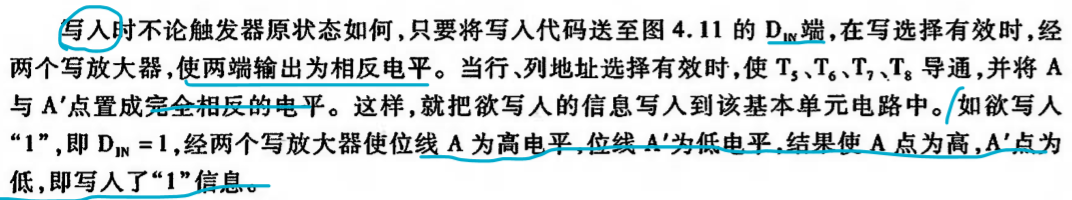

2.3.1 静态RAM

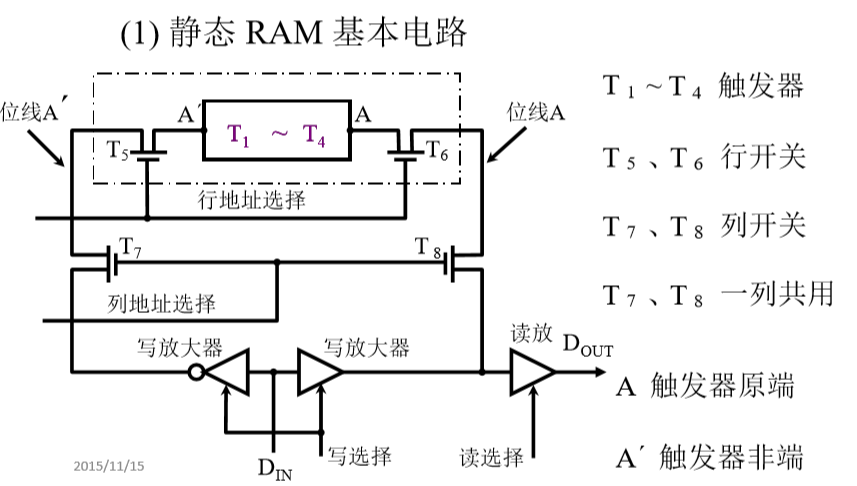

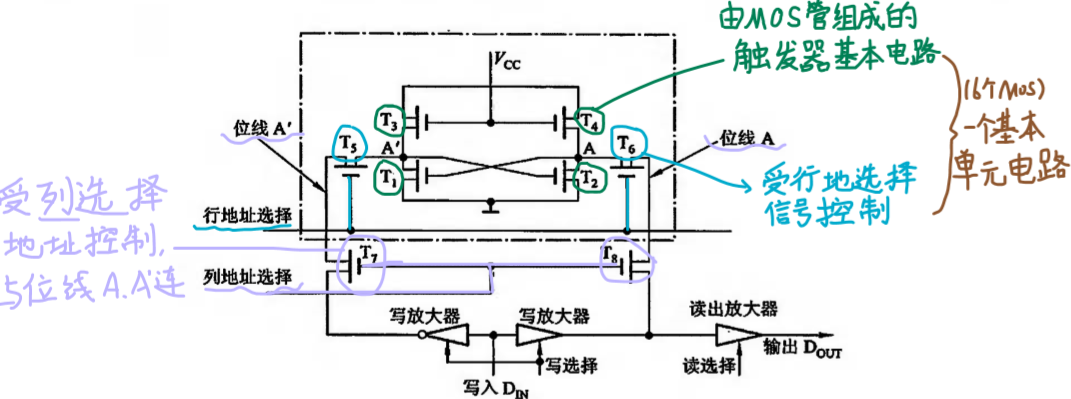

(ⅰ)静态RAM基本单元电路

存储器中,用于寄存0/1代码的电路叫存储器的基本单元电路。(因为记录0/1是基础技能,保存0/1的原理是双稳态触发器)

T1~T4解决了用什么样的电路存放0/1

T5,T6决定是读还是写

虚线框里的存储元件,在实际中会是一列,有好多:T7,T8是控制一列的控制开关

A:触发器原端

A’:触发器非端,就是他们俩之间的数据是相反的

如图,是一个由6个MOS管组成的基本单元电路

## T7、T8不包含在基本单元电路内,而是芯片内,同一列的各个基本单元电路所共有的(??为啥??歧视人家列啊)

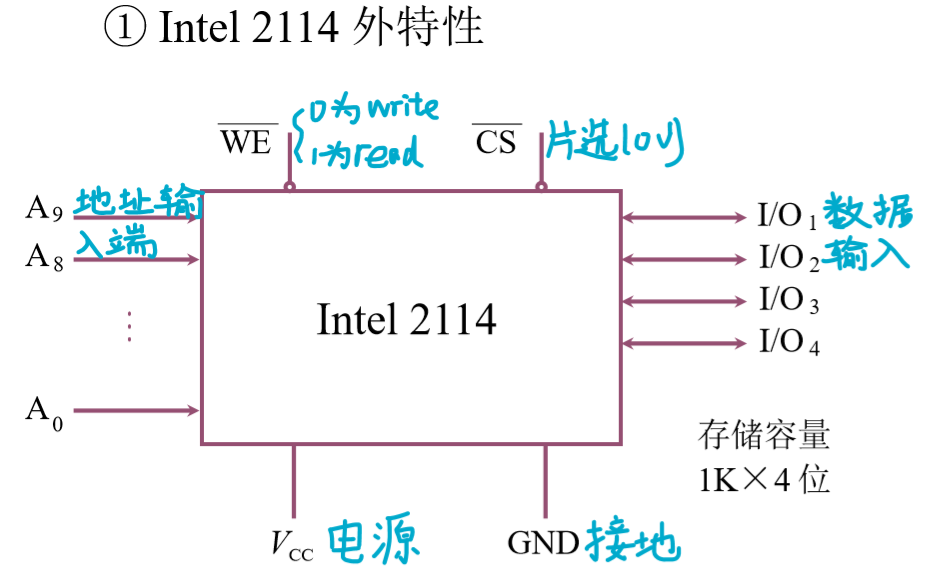

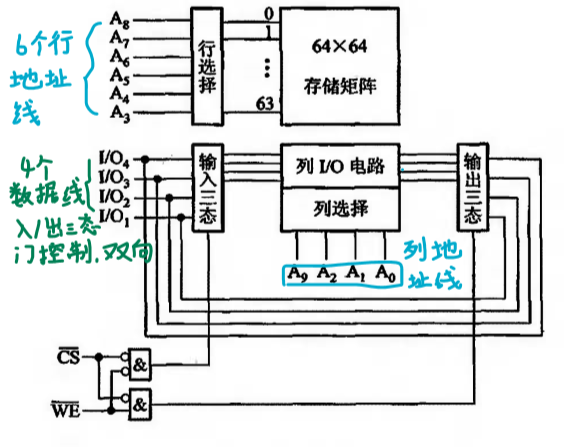

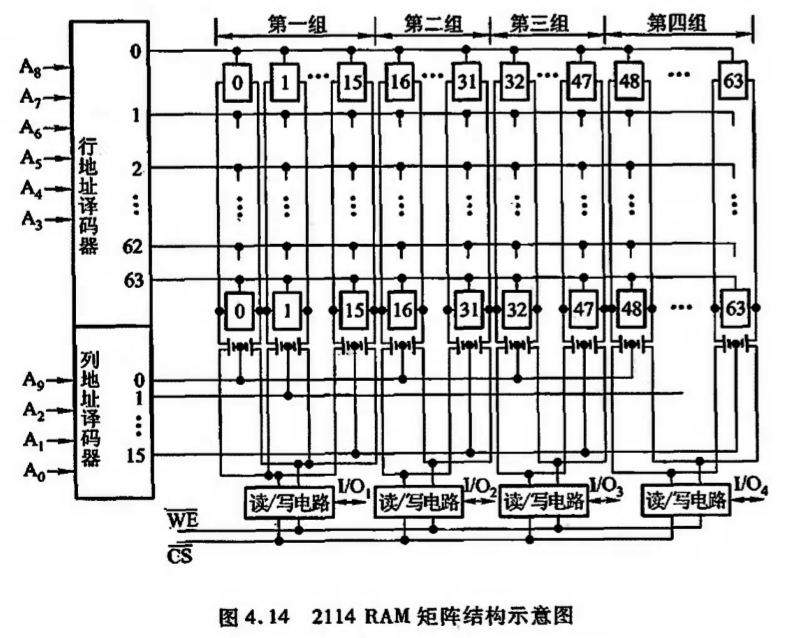

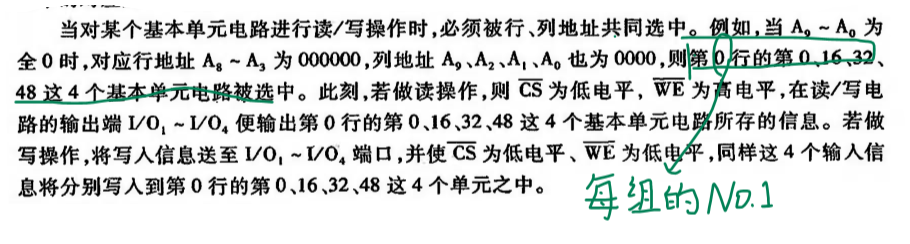

(ⅱ).芯片举例

上图里,每一个小方格均为一个由6个MOS管组成的基本单元电路,排成64*64矩阵,对应64对T7,T8管(一列小方块只需要一对T7&T8),因为读写一次要4个数据,所以要把这64列分成4组,每组16列,一组对应一个读写电路

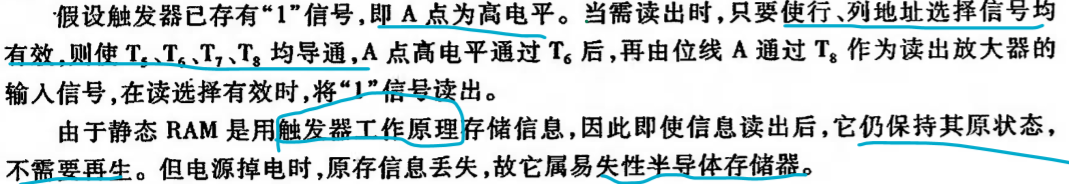

(ⅲ).静态RAM读/写时序

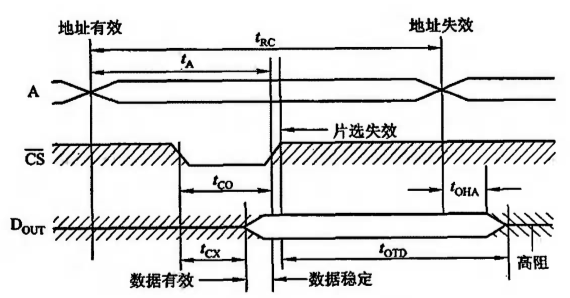

①读周期时序

WE始终为高电平

(应该不是重点,随便瞅瞅)

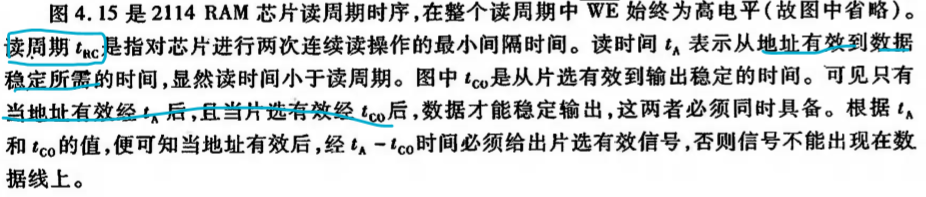

②写周期时序

2.3.2 动态RAM

(ⅰ).动态RAM的基本单元电路

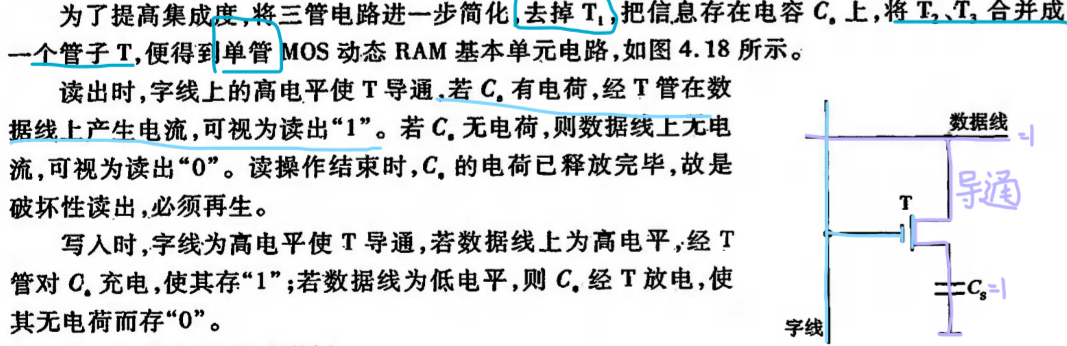

①保存0和1的原理:电容存储电荷,若保存了电荷,即为1;若没有电荷,就是0。电容上的电荷一般只能维持1~2ms,因此即使电源不掉电,信息也会自动消失。为此,必须在2ms内对其所有存储单元恢复一次原状态,叫做再生/刷新。

②与静态相比,集成度更高,功耗更低,被广泛应用

③分为两类:三管式&单管式

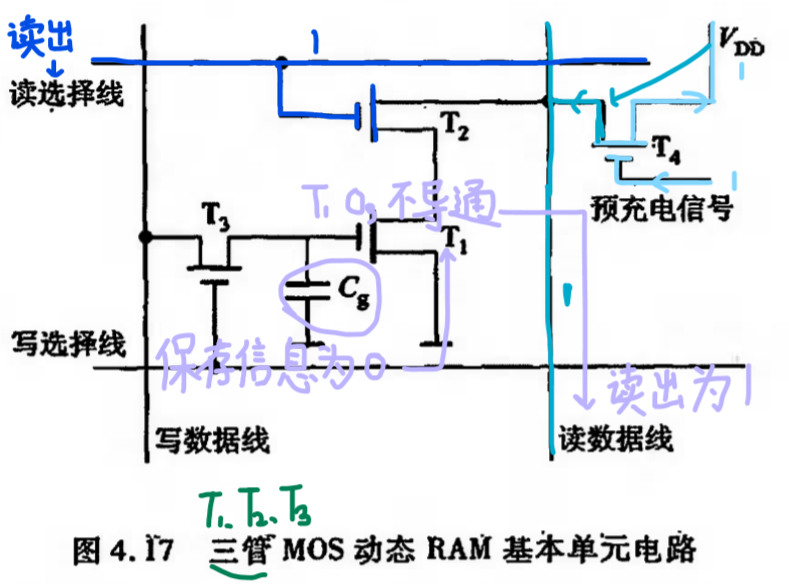

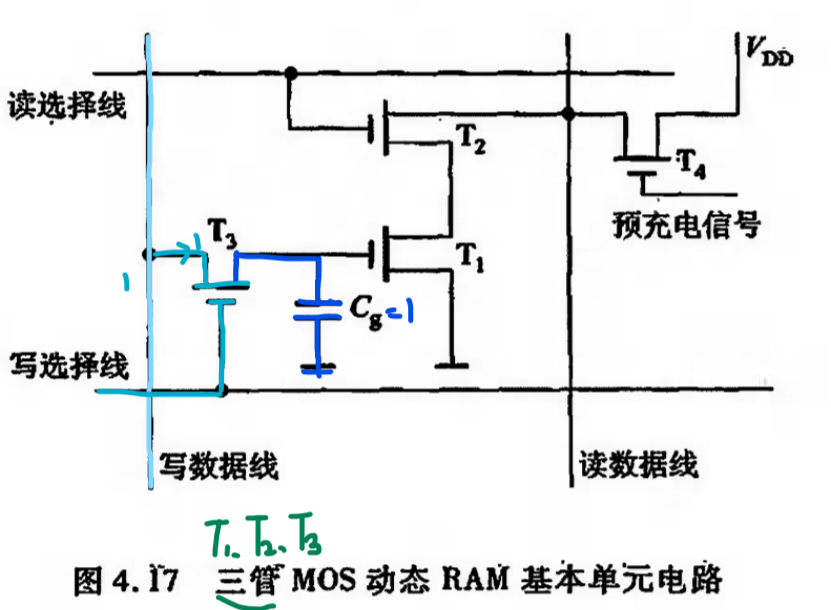

读出时,先对预充电管T4充电,为1(在存储矩阵中,每一列共用一个T4管),使VDD为高电平;然后,读选择线打开T2,⑴若Cg保存的信息为1(就是有充足的电荷),T1,T2导通,接地,使都数据线降为低电平0,读出信息为0;⑵若Cg保存的信息为0(没有电荷),T1截止,读数据线依旧为高电平1。

## 可见,读出与原存数据相反

## 写入相同

(ⅱ)芯片举例

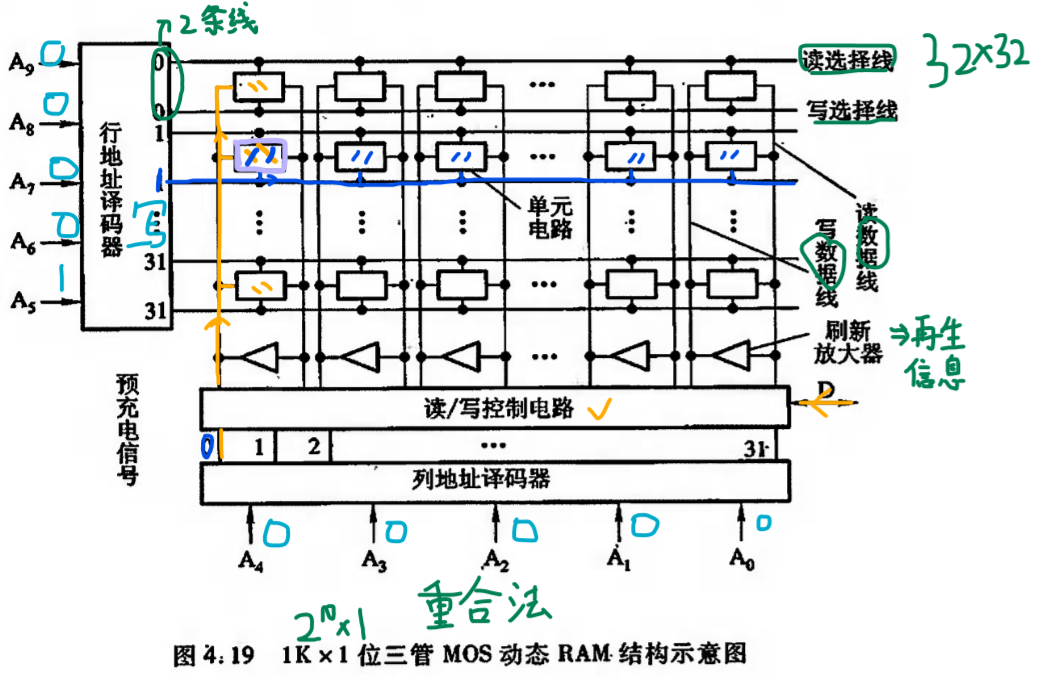

①三管动态RAM芯片

②单管动态RAM芯片

16K=2¹⁴,理应有14根地址线。但为了减小芯片封装的引脚数,地址线只有7根,那他们怎么操作呢?——地址信息分两次传送:先送7位行地址保存到行地址缓冲器;再送7位列地址保存到列缓冲器。

读写时,行列地址受RAS&CAS控制,分两次存入行列地址缓存器。行地址选中后,该行所有MOS管导通,并将其电容Cs上的电荷反映到放大器的另一侧,且变为相反的。至于是相同还是相反,自己判断好啦~~

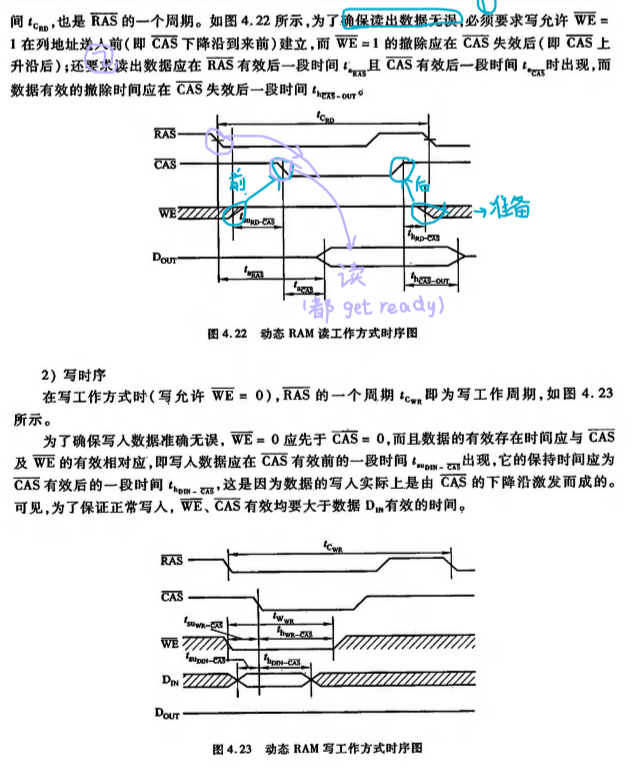

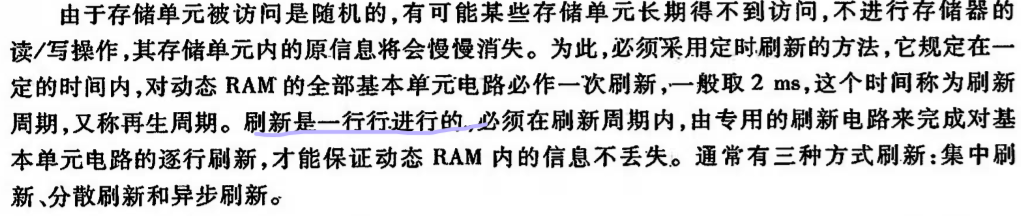

(ⅲ)动态RAM时序

(ⅳ)动态RAM刷新

## 与行地址有关

##实质:把原来的信息读出来,再由刷新放大器形成原信息,重新写入

①集中刷新

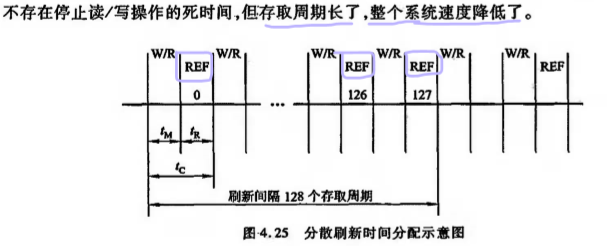

②分散刷新

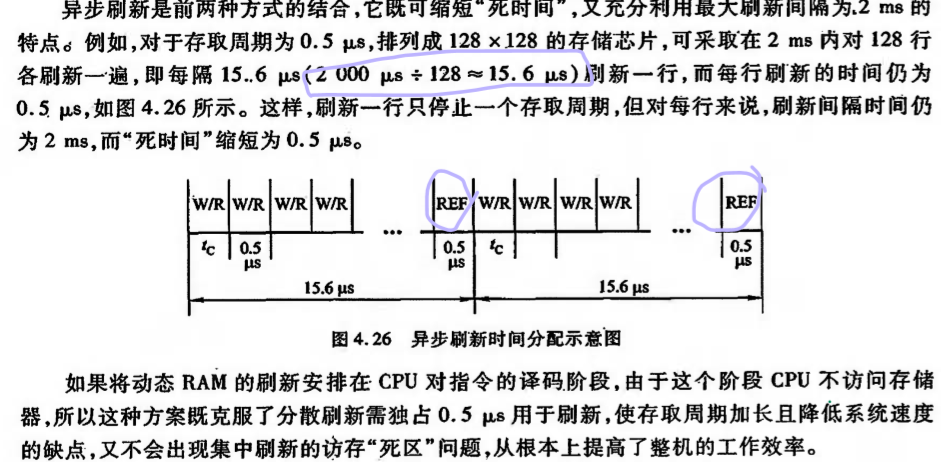

③异步刷新

2.3.3 动态&静态比较