1.前言

- k64 ENET CORE 实现了10M/100Mbps的Ethernet MAC,与IEEE802.3-2002标准兼容。

- MAC层与全双工/半双工的10M/100Mbps以太网兼容;

- MAC操作可实现全编程,可以用在网络接口卡、bridging,switching applicaton

- The core implements the remote network monitoring (RMON) counters according to IETF RFC 2819 ??

- ENET CORE实现了网络加速模块优化TCP/IP,UDP,ICMP协议服务的网络控制器的性能

- CORE提供了可编程的FIFO,这样可以在接收数据时缓存数据保证数据流的无损传输

- 先进的电源管理特性

- MAC符合IEEE 1588标准,集成了时间戳模块,IEEE1588为分布式控制节点提供了精准时钟用于工业自动化应用

2.特性

2.1 ETHERNET MAC特性

实现了802.3规范的全部内容

支持0长度报文

支持10M/100Mbps动态配置

符合AMD magic包中断检测

支持如下接口的PHY:

(1)a 4-bit Media Independent Interface (MII) operating at 25 MHz.

(2)a 4-bit non-standard MII-Lite (MII without the CRS and COL signals) operating at 25 MHz.

(3)a 2-bit Reduced MII (RMII) operating at 50 MHz

简单的64bit fifo用户接口

CRC32检测

全双工模式下支持自动停止帧?

半双工提供冲突解决

支持VLAN-tagged 帧

可编程MAC地址

Programmable promiscuous mode support to omit MAC destination address checking on receive

接收时多播和单播地址过滤

可编程帧最大长度

帧传输和错误、停止帧统计信息

简单的握手应用FIFO接口

为每一个介绍到的数据帧提供状态字

多路可选内部loopback

MDIO master接口用于phy设备配置和管理

支持遗留的FEC buffer描述

2.2 IP protocol performance optimization features

1.Operates on TCP/IP and UDP/IP and ICMP/IP protocol data or IP header only

2.Enables wire-speed processing

3.Supports IPv4 and IPv6

4.Transparent passing of frames of other types and protocols

5.Supports VLAN tagged frames according to IEEE 802.1q with transparent forwarding of VLAN tag and control field

6.Automatic IP-header and payload (protocol specific) checksum calculation and verification on receive

7.Automatic IP-header and payload (protocol specific) checksum generation and automatic insertion on transmit configurable on a per-frame basis

8.Supports IP and TCP, UDP, ICMP data for checksum generation and checking

9.Supports full header options for IPv4 and TCP protocol headers

10.Provides IPv6 support to datagrams with base header only — datagrams with extension headers are passed transparently unmodifed/unchecked

11.Provides statistics information for received IP and protocol errors

12.Configurable automatic discard of erroneous frames

13.Configurable automatic host-to-network (RX) and network-to-host (TX) byte order conversion for IP and TCP/UDP/ICMP headers within the frame

14.Configurable padding remove for short IP datagrams on receive

15.Configurable Ethernet payload alignment to allow for 32-bit word-aligned header and payload processing

16.Programmable store-and-forward operation with clock and rate decoupling FIFOs

2.3 IEEE 1588 features

Supports all IEEE 1588 frames

Allows reference clock to be chosen independently of network speed

Software-programmable precise time-stamping of ingress and egress frames

Timer monitoring capabilities for system calibration and timing accuracy management

Precise time-stamping of external events with programmable interrupt generation

Programmable event and interrupt generation for external system control

Supports hardware- and software-controllable timer synchronization

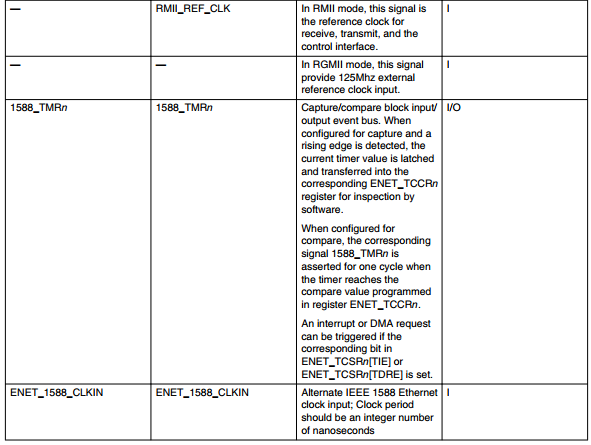

Provides a 4-channel IEEE 1588 timer — each channel supports input capture and output compare using the 1588 counter

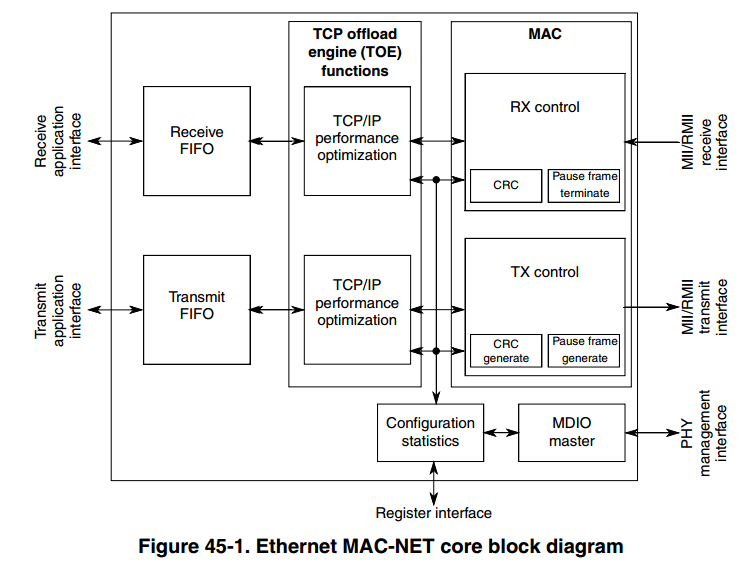

3.Block DIagram

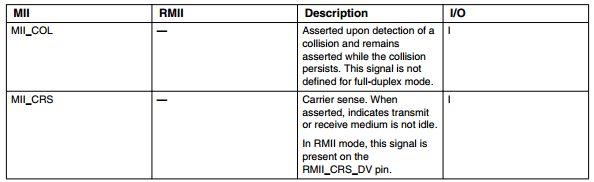

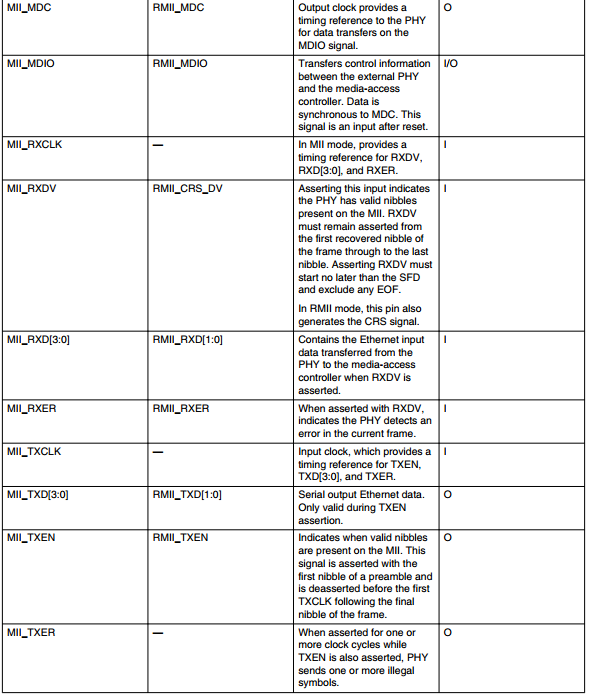

4.信号描述

5.Memory map/register definition

TODO