1.前言

UART实现与外设或CPU的通信

2. UART概述

2.1基本特性

(1)Full-duplex operation

(2)Standard mark/space non-return-to-zero (NRZ) format?

(3)Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse width?

(4)13-bit baud rate selection with /32 fractional divide, based on the module clock frequency

(5)Programmable 8-bit or 9-bit data format

(6)Programmable 1 or 2 stop bits in a data frame.

(7)Separately enabled transmitter and receiver

(8)Programmable transmitter output polarity

(9)Programmable receive input polarity

(10)Up to 16-bit break character transmission.

(11)11-bit break character detection option

(12)Independent FIFO structure for transmit and receive

(13)Two receiver wakeup methods:

Idle line wakeup

Address mark wakeup

(14)Address match feature in the receiver to reduce address mark wakeup ISR overhead?

(15)Ability to select MSB or LSB to be first bit on wire

(16)Hardware flow control support for request to send (RTS) and clear to send (CTS) signals?

(17)Support for ISO 7816 protocol to interface with SIM cards and smart cards

Support for T=0 and T=1 protocols

Automatic retransmission of NACK'd packets with programmable retry threshold

Support for 11 and 12 ETU transfers

Detection of initial packet and automated transfer parameter programming?

Interrupt-driven operation with seven ISO-7816 specific interrupts:

Wait time violated

Character wait time violated

Block wait time violated

Initial frame detected

Transmit error threshold exceeded

Receive error threshold exceeded

Guard time violated

(18)Interrupt-driven operation with 12 flags, not specific to ISO-7816 support

Transmitter data buffer at or below watermark

Transmission complete

Receiver data buffer at or above watermark

Idle receiver input

Receiver data buffer overrun

Receiver data buffer underflow

Transmit data buffer overflow

Noise error

Framing error

Parity error

Active edge on receive pin

LIN break detect

(19)Receiver framing error detection

(20)Hardware parity generation and checking

(21)1/16 bit-time noise detection

(22)DMA interface

2.2 操作模式

- run mode

normal操作模式

- wait mode

UART的操作依赖于C1[UARTSWAI] 域,如果C1[UARTSWAI] 为0则UART正常操作,如果C1[UARTSWAI] 1且CPU在wait mode,UART时钟停止,UART进入低功耗模式

当内部或外部中断唤醒CPU时,会唤醒UART发送或接收

- stop mode

此模式下UART被禁用,当外部中断将CPU退出stop mode时会唤醒UART发送或接收

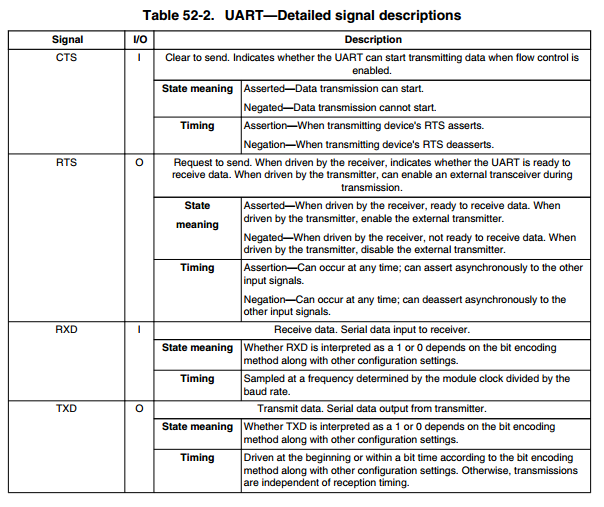

2.3 UART信号描述

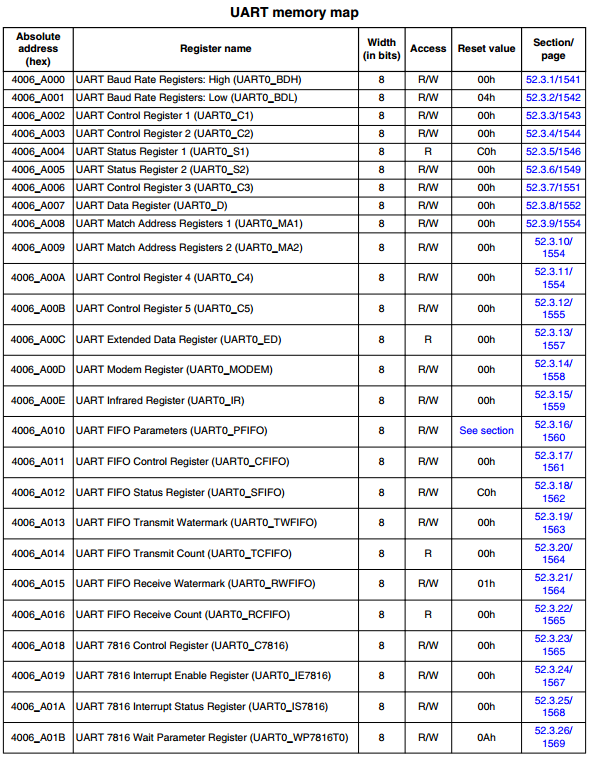

3.Memory map and registers

只支持单字节访问,下面只给出UART0的寄存器:

4.功能描述

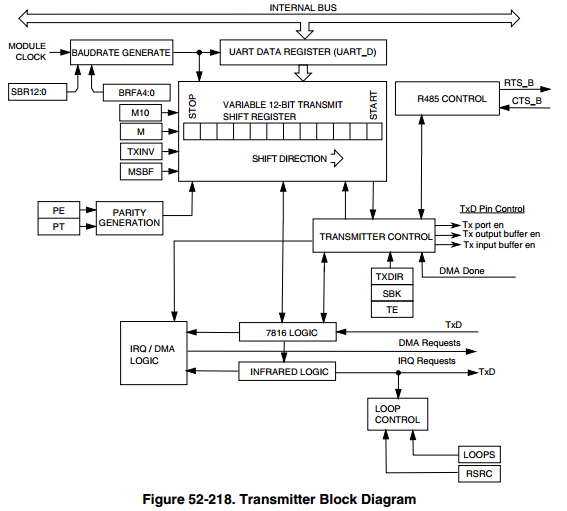

4.1 transmitter

1.支持传输8,9,10数据字符;

2.支持先传输MSB还是LSB可配置;

3.break characters:可以传输break chracters,break chracters包含所有的逻辑0,没有起始、校验位

4.Idle characters: 可以传输idle chracters,idle chracters包含所有的逻辑1,没有起始、校验位

5.Hardware flow control :根据CTS的是否assert来决定是否开启transmitter

6.Transceiver driver enable :??

4.2 receiver

4.3 Baud rate generation

4.4 Data format (non ISO-7816)

4.5 Single-wire operation

4.6 Loop operation

4.7 ISO-7816/smartcard support

4.8 Infrared interface

5.reset

6. System level interrupt sources

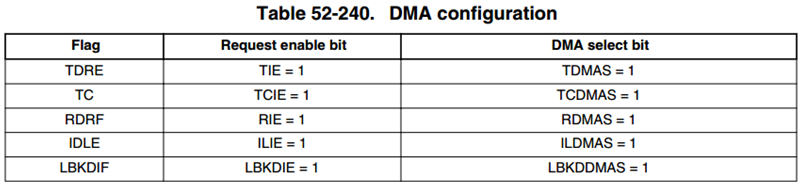

7.DMA operation

在传输时,S1[TDRE] and S1[TC]用来配置为assert一个DMA传输请求;

在接收时,S1[RDRF], S1[IDLE], and S2[LBKDIF]被配置为assert一个DMA传输请求

下面的表显示了DMA请求的相关的flag配置:

当一个flag用来配置为DMA请求,那么如果flag被置位时,与之相连的DMA请求就会assert,直到DMA传输完毕才会deassert DMA请求