1.前言

本文主要讲述K64芯片配置,关于模拟部分的内容,主要包括:ADC, CMP, DAC, VREF

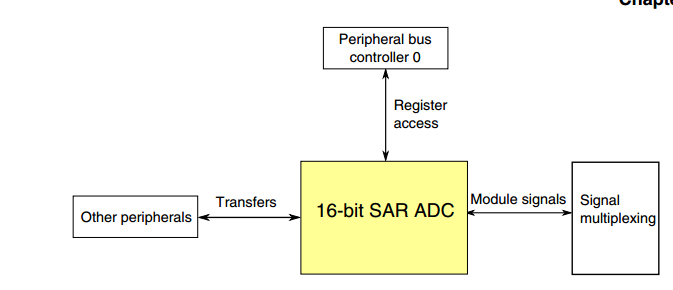

2.16bit SAR ADC

从上图可以看出ADC主要挂在外设总线0上,由于ADC的输入引脚需要做MFP配置,因此与signal multiplexing连接,同时由于其它模块可以触发ADC采集,以及DMA操作,因此也与其它外设关联

2.1 ADC相关信息

1.物理上包含两路ADC

2.关于ADC通道

从ADC框图上可以看出,支持24路单端ADC,四路差分ADC,对应28个输入信号(DADP0~3,DADM0~3,DAD4~DAD23)

2.2 DMA支持

应用请求ADC采样会给CPU带来负担,使用PDB可以触发ADC进行采集减少CPU的负担。

ADC可以在转换完毕后通过发送DMA请求触发DMA传输

2.3 通道连接与指定

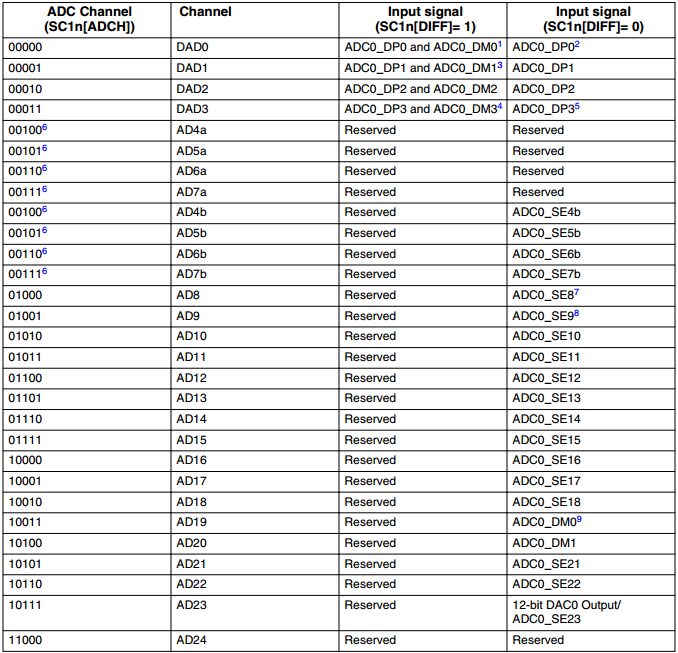

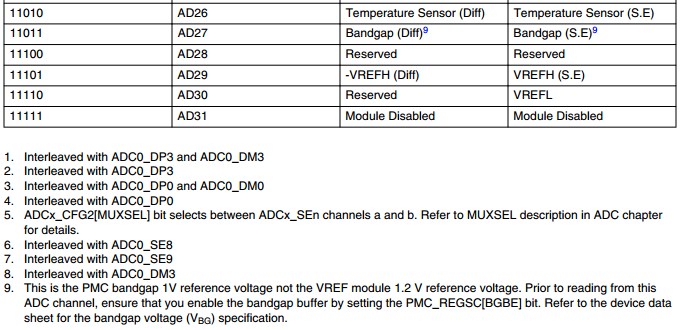

以144pin为例说明,如下是ADC0通道

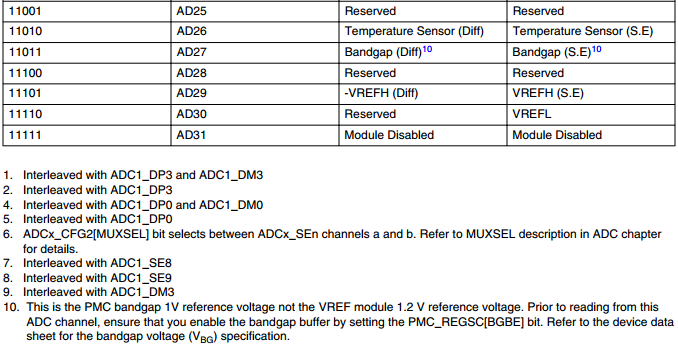

以144pin为例说明,如下是ADC1通道

注:要格外注意上面的注释说明中interleaved的含义,它指的是为了对单个输入达到更高的采样率,因此内部将分派到两路ADC做交错采集

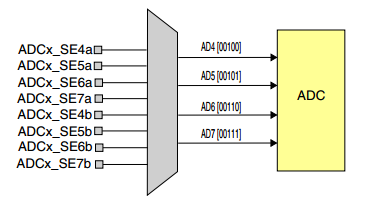

2.4 ADC通道的多路选择

通过配置ADCx_CFG2[MUXSEL] 可以选择a通道还是b通道到达ADC

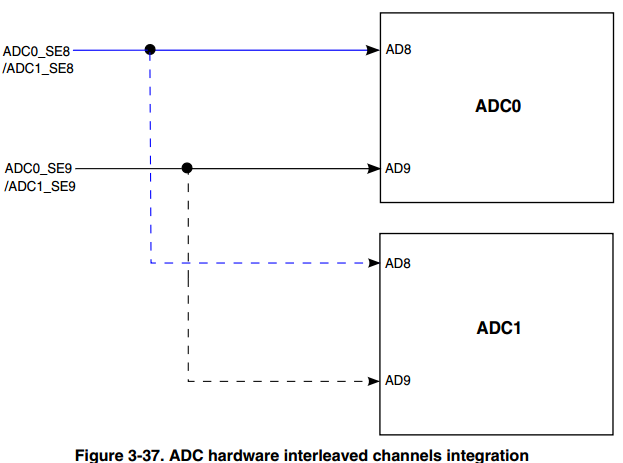

2.5 ADC硬件交错通道

也就是说两个ADC对应了同一个输入引脚,这样通过两路ADC交错对同一路输入进行采集,可以做到高速采集,提高采样速率

2.6 ADC reference选项

支持两种reference:

VREFH/VREFL - connected as the primary reference option

1.2 V VREF_OUT - connected as the VALT reference option

2.7 ADC Triggering

1.支持软件和硬件trringger,主要的硬件 trrigger是PDB,PDB也可以被其它模块触发,如RTC

2.ADC也可在低功耗模式下作转换,ADC转换完毕产生中断唤醒系统,PDB也可以通过ADCxTRGSEL 忽略掉

不同模式下的trrigger参考单元管理章节

2.8 可选时钟

2.9 ADC低功耗模式

芯片的各种低功耗模式下对应的ADC模块的工作模式

3. CMP配置

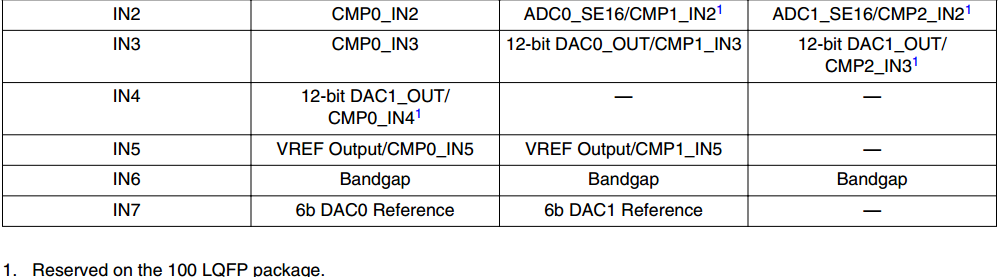

3.1 CMP输入连接

下图显示了CMP输入连接

3.2 CMP外部参考

TODO

3.3 外部windole/sample输入

由专门的PDB模块控制每个CMP采样/窗口和时序

4. 12bit DAC配置

TODO

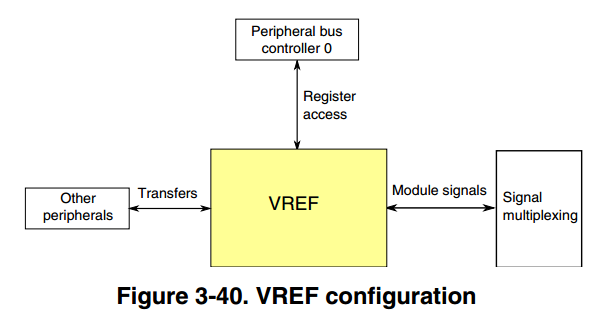

5.VREF配置

5.1 概览

包含一个VREF提供精准1.2v电压输出,可以给外设提供参考或者给模拟外设提供参考,比如ADC,DAC,CMP

注:请主要datasheet中注释部分