1.前言

每个GPIO端口有如下几个寄存器进行操作:

- 两个32位配置寄存器:GPIOx_CRL, GPIOx_CRH

- 两个32位数据寄存器:GPIOx_IDR, GPIOx_ODR

- 一个32位set/reset寄存器:GPOx_BSRR

- 一个16位reset寄存器:GPIOx_BRR

- 一个32位锁定寄存器:GPIOx_LCKR

注:GPIO_BRR和GPIO_BSRR支持读写的原子访问

每组GPIO的 port可以配置成如下的IO方式:

2.GPIO基本结构

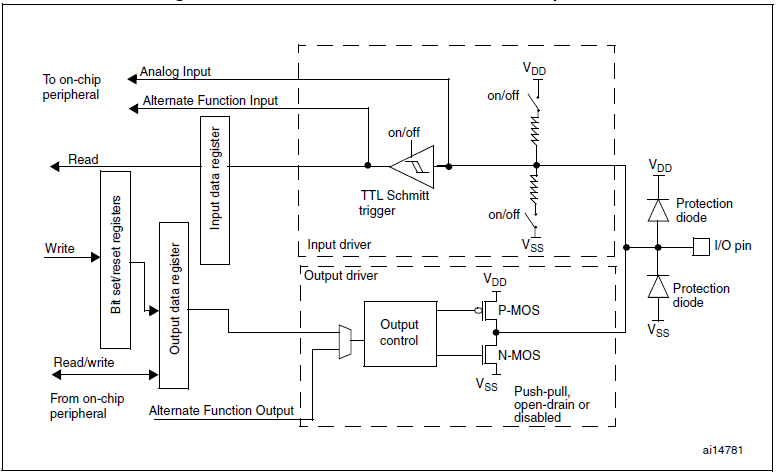

图 标准GPIO位的基本结构

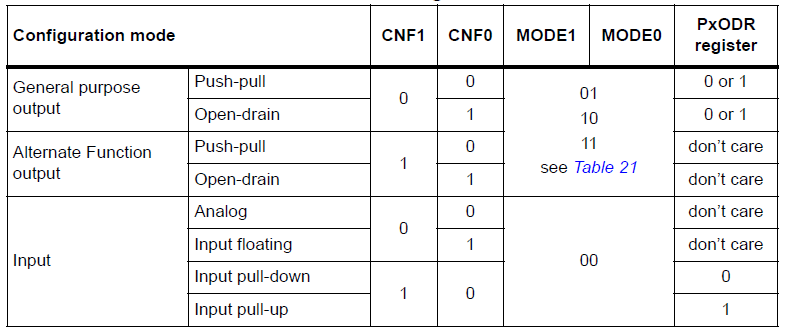

图 port bit配置表

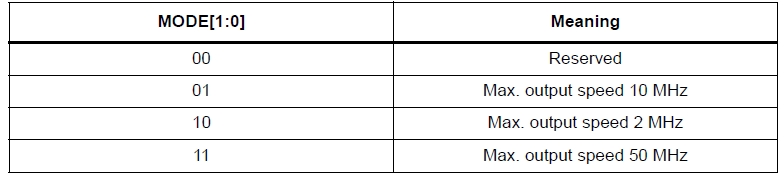

图 输出模式bit

3.GPIO功能描述

3.1 通用目的IO(GPIO)

- reset过程中或刚reset后

引脚的可选功能是无效的,端口被配置成Input Floating Mode(CNFx[1:0]=01b, MODEx[1:0]=00b).

RESET后JTAG pin:PA15: JTDI in PU 、 PA14: JTCK in PD 、 PA13: JTMS in PU 、 PB4: NJTRST in PU

- 配置为输出模式

写到GPIOx_ODR中的值被输出到port引脚,可能使用的驱动模式:push-pull or open-drain

- 配置为输入模式

GPIOx_IDR在每个APB2时钟周期会捕获IO引脚上的数据

注:1.每个GPIO PIN都有一个弱上拉和一个弱下拉,在配置为输入模式时可以决定是否使能

- 原子的bit set/reset

在操作GPIO_ODR寄存器的时候没有必要关中断,通过写入GPIO_BRR或GPIO_BSRR来set或reset GPIO的相关port bit

- 外部中断/唤醒线

所有的gpio端口都具有中断/唤醒功能,要使用外部中断线,需要配置为输入功能

- IO配置锁定功能

当配置锁定功能后,GPIO的port bit将不能修改,除非reset

- GPIO寄存器说明

GPIO_CRL:设置GPIO低8个port bit的输入/输出模式、设置driver方式;

GPIO_CRH:设置GPIO高8个port bit的输入/输出模式、设置driver方式;

GPIO_IDR:显示每个GPIO port的输入值

GPIO_ODR:设置每个GPIO port的输出值

GPIO_BSRR:标记输出值寄存器的哪些位需要set/reset

GPIO_BRR:标记输出值寄存器的哪些位需要REset

GPIO_LCKR:设定GPIO的哪些port bit配置被锁定

3.2 可选功能(AF)

- 可选功能输入

port必须配置为输入模式(input floating, input pull-up, intpu pull-down),且输入pin必须由外部驱动

- 可选功能输出

port必须配置为输出模式(push-pull or open-drain)

- 可选功能双向

在输出时,port必须配置为输出模式(push-pull or open-drain);在输入时port必须配成输入模式(input floating)

注:1. 配置一个 port为可选功能输出,则会断开输出寄存器,并与外设的某个输出信号引脚链接,如图 标准GPIO位的基本结构

2. 如果软件将GPIO配置为可选功能输出,但是外设没有使能,这输出状态不确定

- 软件重现映射I/O可选功能

通过配置AFIO寄存器,重映射一些功能到其它引脚,此时这些可选功能将与原有GPIO断绝关联

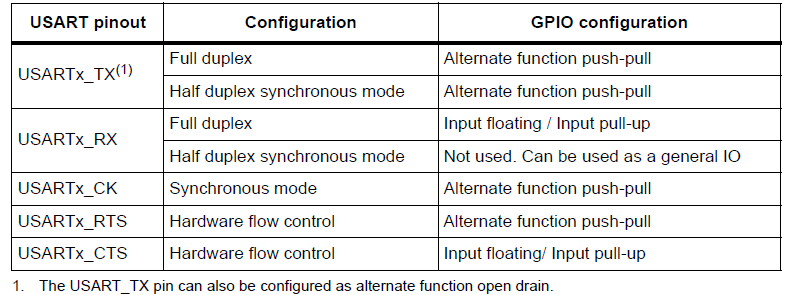

- 举例:配置为UART功能

- AFIO寄存器说明

AFIO_EVCR:如果置位,cotex事件将发送到某个端口的pin

AFIO_MAPR/AFIO_MAPR2:对可选功能进行重新映射

AFIO_EXTICR1/AFIO_EXTICR2/AFIO_EXTICR3/AFIO_EXTICR4:设置各个GPIO的中断线

4. 参考文献

[1] STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and

STM32F107xx advanced ARM®-based 32-bit MCUs