时钟控制执行顺序

设计中需要像C/C++语言的串行控制功能,如先接收外部配置指定,然后接收数据并完成模块内部配置,再将配置结果反馈到外部,这需要通过时间的精确定位来获取严格的先后关系。 那么怎么来实现呢其实很简单,假设全部事件需要5个时钟周期,那么利用一个周期为5的循环计数器来实现。在计数器为1的时候,完成事件1;在计数器为2的时候,完成事件2:……如此循环即可。总结起来就是按照时钟节拍来完成串行控制。当然,这样的电路在FPGA资源的利用上是存在浪费的,因为在执行事件1,用于执行事件2,3,4,5的逻辑处于等待状态,但其却始终占用着逻辑资源,也就是这部分电路没有使能,但是依然存在于FPGA内部。

实例分析·

请看如下代码,建议手动输入到ise里面,动手综合后看看实现的RTL图,看懂电路原理。

-

module clk_module(clk,reset,a1,y1,y2);

-

-

input clk;

-

input reset;

-

input [7:0] a1;

-

output [7:0] y1,y2;

-

-

reg [7:0] y1,y2;

-

reg [1:0] cnt;

-

always@(posedge clk)begin

-

if(!reset)begin

-

cnt <= 0;

-

y1 <= 0;

-

y2 <= 0;

-

end

-

else begin

-

if(cnt == 2'b11)

-

cnt <= 2'b00;

-

else

-

cnt <= cnt + 2'b01;

-

//------------//

-

case(cnt)

-

2'b00:begin

-

y1 <= a1 + 2'b01;

-

y2 <= y2;

-

end

-

2'b01:begin

-

y1 <= y1;

-

y2 <= y1 + 2'b01;

-

end

-

default:begin

-

y1 <= y1;

-

y2 <= y2;

-

end

-

endcase

-

end

-

end

-

-

endmodule

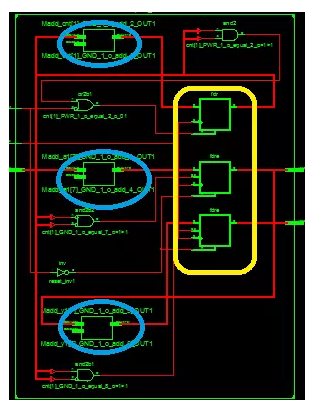

上述代码综合后RTL图如下,浅蓝色圆圈圈住的是生成的3个加法器,就是计算cnt和y1,y2的3个加法器。黄色方框里面的是触发器,负责将结果输出和反馈到加法器输入。

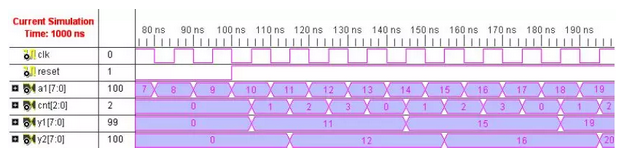

仿真的波形图如下图,可以看出,每4个时钟周期计算一次结果,y1永远比y2提前一个时钟周期出结果,y1的值永远在捕捉到cnt=0的一个上升沿更新,y2永远在捕获到cnt=1的上升沿更新。这也是造成y1提前一周期的原因,所有的状态翻转都是根据cnt的状态变化来的,而cnt的变化是时钟节拍决定的。大家理解好这个例程,也就明白了如何用时钟操控电路,按照你的想法去运行,同时学会了一段式状态机的应用。

转载自微信玩转FPGA