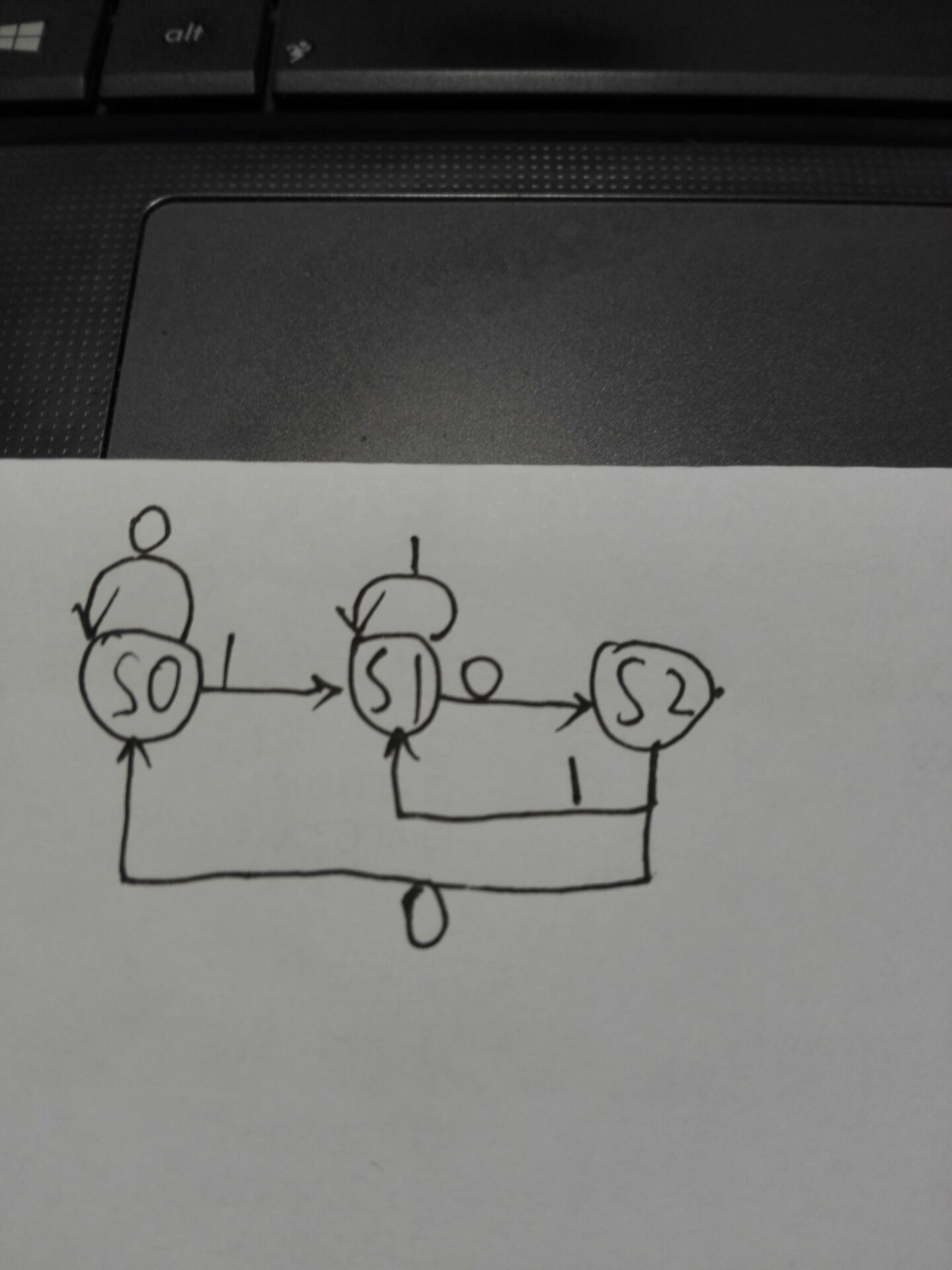

比如序列检测101,需要三个状态 :so,s1,s2。

思路:(1)s0状态有两种情况0或1,若为0时在自身打圈,是1时进入s1状态。

(2)s1状态有两种0或1,若为1自身打圈,因为1可以作为下次检测101的起始,有用信号,相当于s0自动进入s1所以自身打圈。若是s1是0则进入下个状态s2,。

(3)s2为0时则s0,s1,s2:1,0,0。由于00不能再利用故从头再来进入s0状态。若s2为1那么101检测完毕输出想要的结果即可,因为1可以利用作为下次检验101中的0,因此进入检验0的状态,

所以进入s1状态检验下次是否为0。。以上每个状态的0或1均考虑清楚了。

编写verilog hel程序即可;

/************************************************

>>>>>>>>>>>>>>>>copyright notice<<<<<<<<<<<<<<<<<

module serial_detect

author:shiguanghua

description:serial state detect 使用状态机来写代码

date:2016.7.6 15:47

************************************************/

module serial_detect

(

input clk_in,

input rst_in,

input data_in,

output led1,

output reg led2

);

parameter CUNT_NUM=12500000;

reg clk_1hz=0;

reg[24:0] cnt=0;

always @(posedge clk_in or negedge rst_in)

begin

if(!rst_in)

begin cnt<=0; clk_1hz<=0; end

else if(cnt>=CUNT_NUM-1) begin

cnt<=0; clk_1hz<=~clk_1hz; end

else cnt<=cnt+1;

end

parameter s0=0,s1=1,s2=2;

reg[1:0] state=0;

always @(posedge clk_1hz or negedge rst_in)

begin

if(!rst_in) begin state<=s0; led2<=0;end

else

case(state)

s0: begin

if(data_in==0) begin state<=s0;led2<=0; end

else begin state<=s1;led2<=0; end

end

s1: begin

if(data_in==1) begin state<=s1; led2<=0;end

else begin state<=s2; led2<=0; end

end

s2: begin

if(data_in==1)begin state<=s1;led2<=1;end

else begin state<=s0;led2<=0;end

end

default: state<=s0;

endcase

end

assign led1=clk_1hz;

endmodule

下面练习下检测1011序列