在 lattice_ddr3调试经验分享(一)建立工程与仿真 博客中已经实现工程的建立以及仿真。后来公司还真的需要用lattice的FPGA。所以需要对这个example进行分析了。

打开 test_mem_ctrl.v 这个就是tb的顶层了。当然,lattice的很多东西和xilinx的没法比,代码质量也是一样的。lattice除了便宜其他都不好。然而.......... 好了,言归正传,不吐槽了。lattice中例化的ddr是没有设置得像xilinx(xilinx用的是官方仿真模型)的模型一样可以在log中看出你的读写时间,读写地址,读写数据,以及命令。lattice的仿真模型像刚毕业的学生写的一样 —— log里啥都没有,一切自己看波形。

折腾了好久,想自己把镁光官方module放进去,失败!有知道怎么放进去的攻城狮还请赐教了。

万般无奈之下,还是好好分析lattice自己的example

平台:

lattice Diamond3.5 + modelsim10.2c +ecp3 -8 + MT41K64M16TW-107

1,test_mem_ctrl 这个modelsim中屏蔽掉自己不想要的 monitor,odt_watchdog。

还有两个

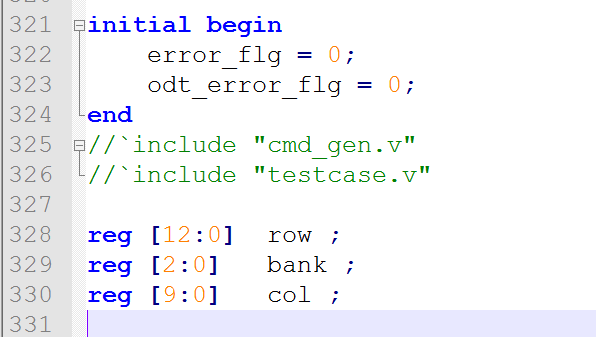

对于325,326两行,是task以及调用task的case。这个写法有些像IC设计的时候做验证的方式。但是我也是做过IC的人,团队中没有人写得这么稀烂过。屏蔽屏蔽!!

然后自己写个这个东西

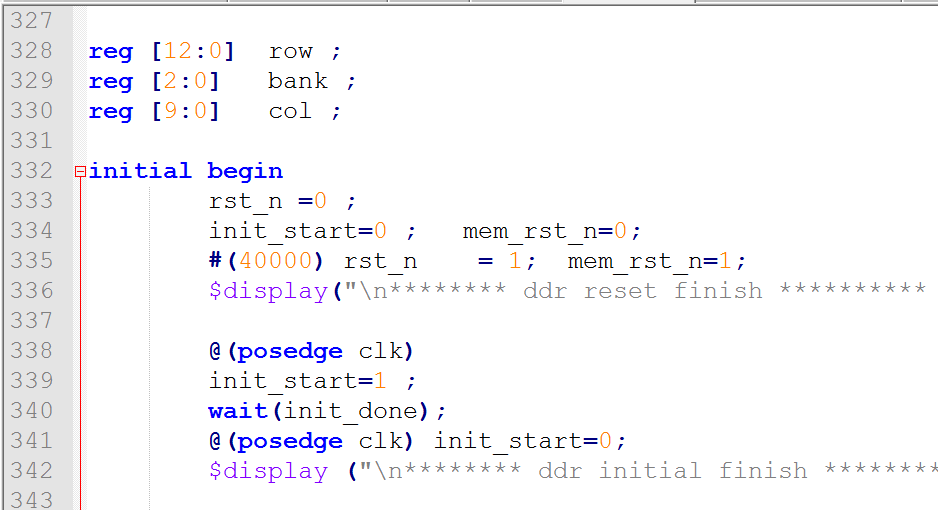

好了,初始化成功了。

这么写肯定会提示reset时间不够,reset到cke的时间不够。先不用管

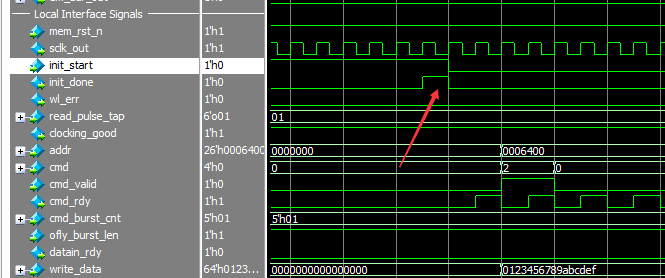

init_start为1,IP核还是初始化ddr。然后重点就是这个init_done拉高一个脉冲。init_start一定要在init_done拉高的一周周期后立刻拉低,不然这个IP又来初始化一次。

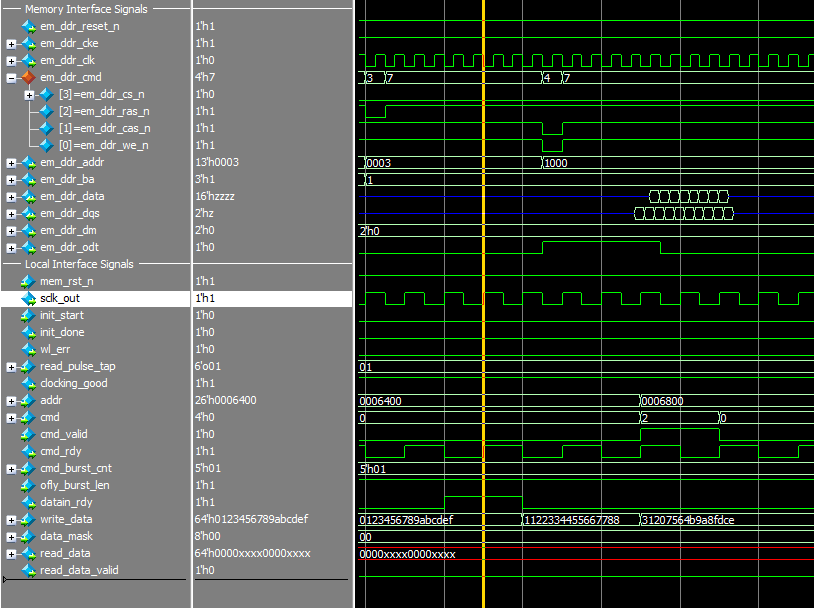

还有几个参数需要注意:ofly_burst_len=1,选择BL8模式

cmd_burst_cnt 这个是命令重复次数。 次数设定在0~32次之间可选。当cmd_burst_cnt =0 你写一次命令,这个IP 就可以重复32次

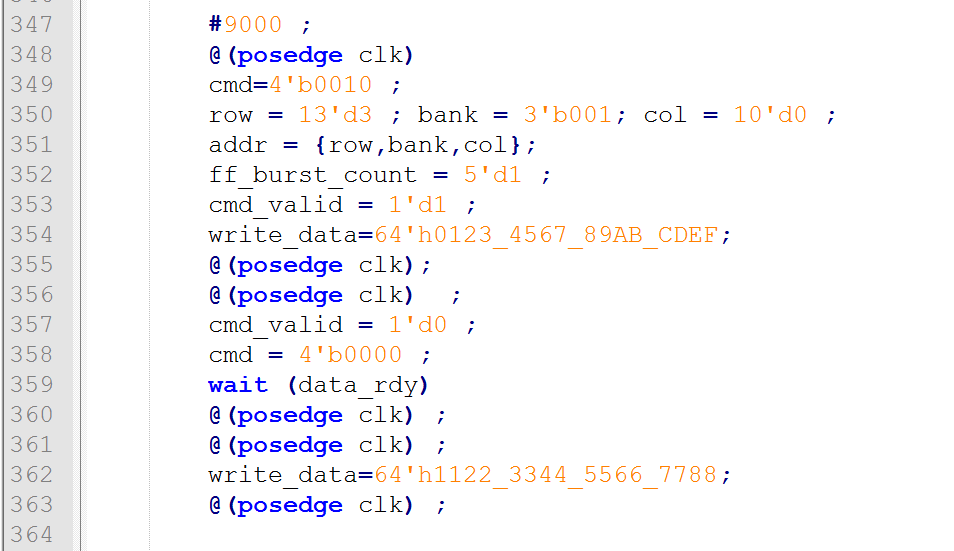

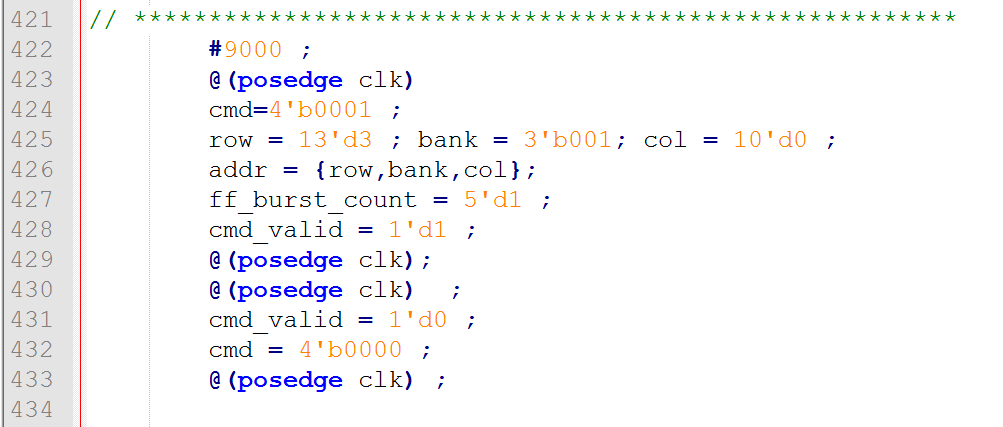

2, 先写,不过这个不可综合的语句我写的有些复杂

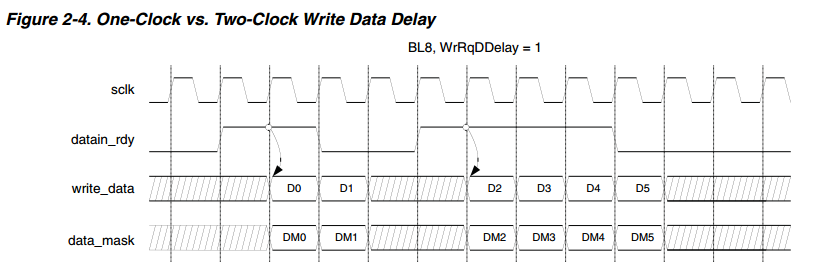

我是随便往里面写了两个数。是不是觉得有些奇怪,为何代码是这样子的。那是因为这个IP里面有一个设定,就是写有效到吃写的数据之间是有latency的,方便大家用fifo。手册上的波形图如下:

然后坑爹的要看波形图了

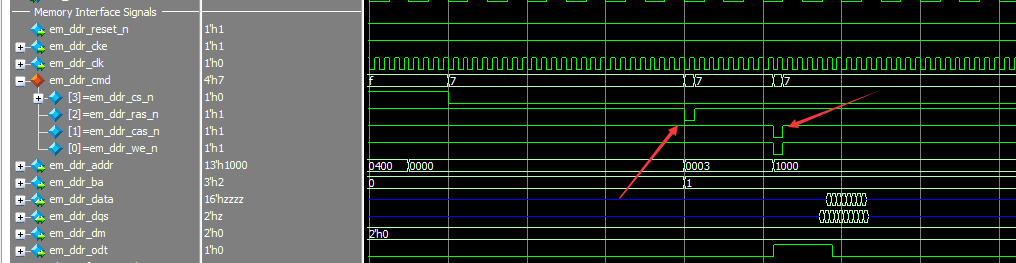

第一个箭头的地方ddr的cmd为0011 是ACTIVE 。后面就是cmd=0100 WRITE —— ddr的datasheet上

看到我写入的地方是bank1,row3 ,col=0 。col在波形图上是 0x1000,要知道col只有10bit。

写的时候需要注意。这个控制器比较坑爹,因为我这个DDR的data位宽是16bit,也就是每个地址只能存16bit数据,然后这个控制器的data接口就成了64bit。要知道每次写地址会自动益增8,也就是每次你应该放进去的数据为16bit*8=128bit,可是控制器的数据位宽只有64bit —— 少了一半,也就是说你每次写应该写两个数据进去,这无疑是降低了控制器的效率啊。

图中黄线部分后是读取的第一个数,再后面的1122334455667788是第二个数。

3,读。读的话就比写简单一些

好了。现在想想怎么把这个模型转换成自己想要的可综合模块吧。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884