应用笔记 V1.0 2015/03/26 | PC和FPGA间的串口通信实现 |

概述 |

本文将介绍PC和FPGA间的串口通信实现的基本思路和Verilog代码,对于通信而言,收发双方都要有相应的控制。PC端采用MATLAB控制串口进行操作。本文档将详细介绍这一过程。 |

修订历史 | 以下表格展示了本文档的修订过程

|

简介 |

PC端程序基于MATLAB 2014a 编写,本文档中提到的"MATLAB"均指该特定版本MATLAB。 为何要做一套PC和FPGA之间通信的程序?之前的文档,包括《程序说明:MATLAB串口操作和GUI编程》和《应用笔记:采用FPGA实现UART转SPI》说明可以通过PC来"控制"FPGA进行相应的操作。在LDPC译码误码率仿真过程中,我们希望通过FPGA强大的计算能力来辅助计算,这时我们希望要能够完成PC传送数据,FPGA处理后发送回PC机的过程。本文档将介绍通过串口完成这一功能的整个过程。 当然,更广泛的来说,数据的处理过程,就应该包括数据的输入和输出。也就是说,对于FPGA来说,很多情况下必须要考虑将外界的数据接收、缓存、处理、缓存、输出的整个过程。这里数据的来源不仅仅能是PC,数据的格式或协议不仅仅能是串行通信协议。也就是说,本文档所介绍的是这一过程的一个特例。 本文档关注FPGA端的处理,对PC端处理不做详细说明。FPGA端处理包括

其中数据接收和发送采用串行通信协议,帧格式如图 1。

图 1 串行数据帧格式 PC端通过MATLAB操作串口,仅仅只需要采取如下命令即可 s=serial('COM1'); fopen(s); fwrite(s,100); %写一个字节 fread(s,[1 1],'unit8'); %读一个字节 fclose(s); delete(s); |

程序结构 |

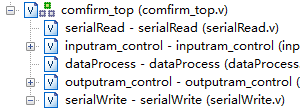

程序结构如图 2所示

图 2 程序结构示意图

顶层文件仅仅只需要如下几个端口 input clk; //时钟 input rxd; //串口输入 input rst; //复位,高有效 output rxt; //串口输出 即输入输出数据即可。后文将详细介绍各个模块的功能。

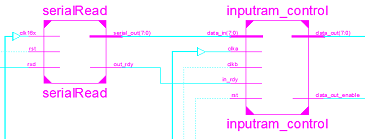

图 3 数据读取、缓存

serialRead的输入时钟是16倍的波特率(时钟不同源),输出的是8bit的并行数据,同时有输出有效的表示。此时输出的时钟也是16倍的波特率。 然而往往数据的处理模块的时钟是不同的。对于隔离时钟域来说,FIFO是一个很好的选择,但是这里由于考虑到译码需要接收到所有的数据之后才能够开始,而且数据在整个译码过程中需要保持,所以选择了双口RAM来匹配不同速率的数据。当然还有一个原因是我不太记得FIFO这个核则么用了。 inputram的clka是16倍的波特率,通过输入地址控制,每次接收到out_rdy有效后地址增1将data_in保存到RAM内部。Inputram的clkb是数据处理模块的时钟,通过相应的规则控制ram的addrb,控制data_out和data_out_enable信号,得到满足数据处理要求的数据流。

图 4 数据处理模块

数据处理模块接收数据后处理输出data_out和data_out_enable

图 5 数据缓存输出

数据处理模块通过接收并存储data_out后,在满足一定条件下发送dout和dout_enable信号。其中clka为数据处理模块时钟频率,而clkb是1/16的波特率的频率。 serialWrite模块通过接收信号,在输出使能情况下,输出rxt。 |

信号说明 |

表格 1 confirm_top模块信号说明

表格 2 serialRead模块信号说明

剩余模块比较简单,不做说明,我也懒得写了…… |

参考 |

|

代码 |

注:以下代码介绍2560个PC的8bit的帧,之后处理取后1024帧的最高数据为,分为128帧传送回PC端。MATLAB代码略。

|