数字asic流程实验(二) CIC滤波器原理简述

1.概述

本次实验需要实现的数字ASIC为一个CIC滤波器,CIC滤波器是一种FIR数字滤波器,其优点为结构简单,与一般的FIR数字滤波器相比,不需要大量的乘法器,只需要加法器和延时,大大简化了运算过程,也不需要存储器保存滤波器系数;其缺点为无法灵活设计幅频特性,因此有时会在抽取的后级加FIR滤波器来整形。CIC滤波器由积分器和梳状器组成,根据级联顺序可以作为抽取滤波器或者插值滤波器来使用。本次实验所实现的CIC滤波器为抽取滤波器。

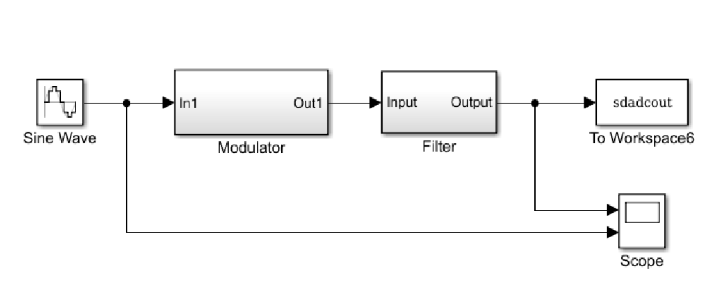

CIC滤波器可用于∑-Δ型ADC中作为数字滤波器。上图为一个∑-Δ型ADC的内部结构,由∑-Δ调制器和CIC数字滤波器构成。CIC滤波器的工作目标是将∑-Δ调制器输出的高频率一位码流转化为较低频率的多位量化值。

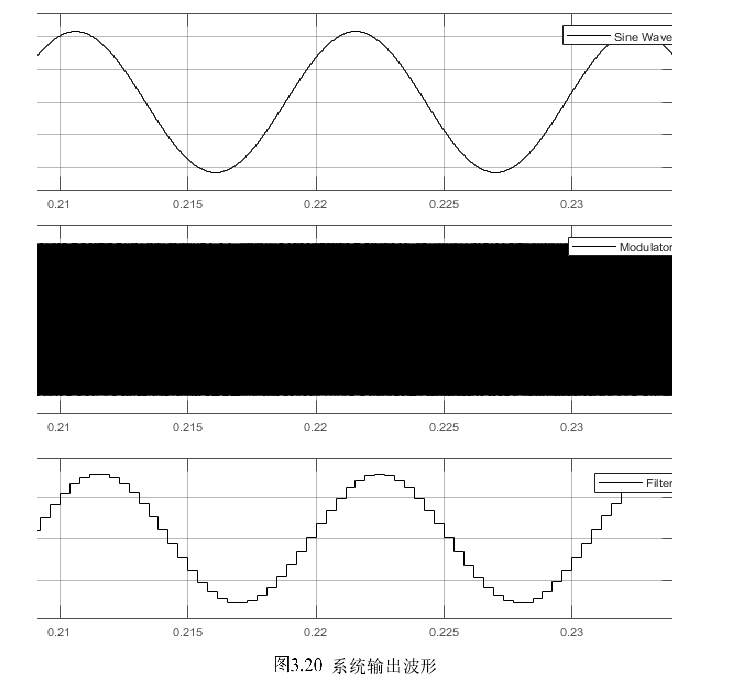

上图中,第一个波形为输入∑-Δ型ADC的正弦波模拟信号,第二个波形为∑-Δ调制器输出的高频率一位码流,第三个波形为经过CIC滤波器后输出的多位量化值。

2.∑-Δ调制器

强烈推荐一下B站up主TerayTech的视频(链接见参考资料部分的b站视频链接),讲的非常形象和清楚,推荐想要对模型有更深刻的理解的读者去看一看。本章节只对∑-Δ调制器的结构、输出结果和工作原理做一个简单的介绍。

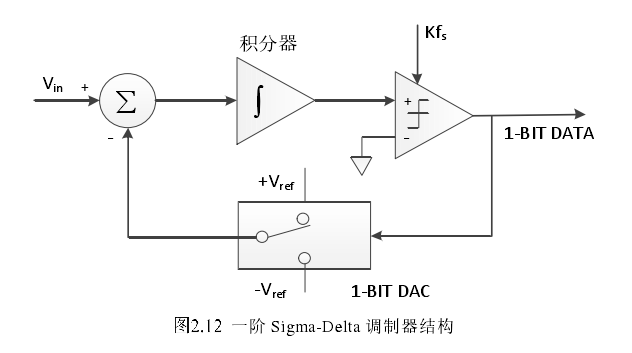

∑-Δ调制器由积分器(sigma),比较器,1bit DAC和求差电路(delta)构成,调制器输出的1bit量化结果通过DAC转化成模拟量并反馈回到输入,其电路结构图如下。

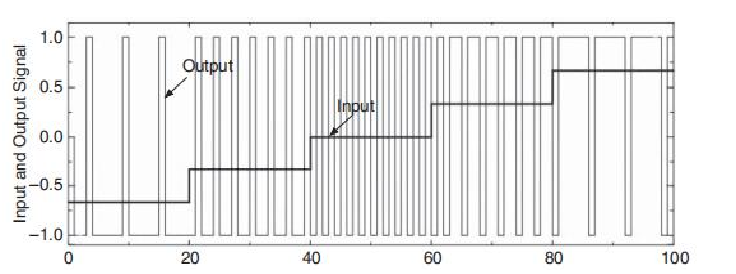

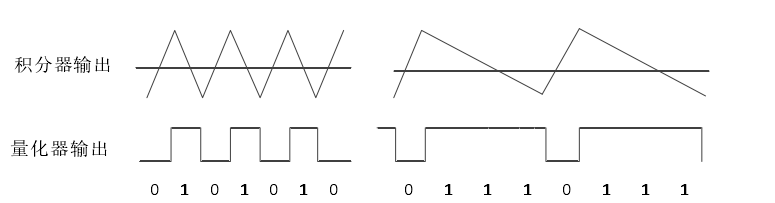

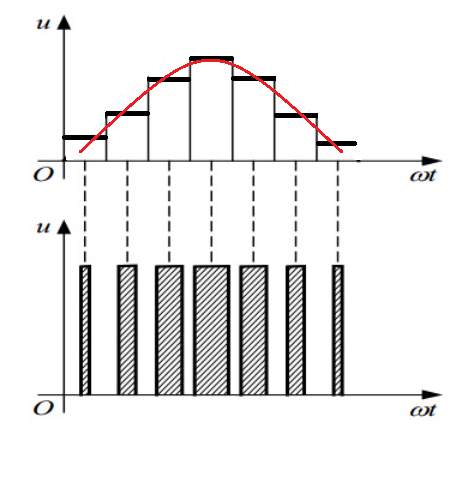

当输入逐渐靠近 (V_{ref})时,输出码流的逻辑"1"数量增加,脉冲宽度越来越宽;当输入逐渐靠近(-V_{ref})时,输出码流的逻辑"0"数量增加,脉冲宽度越来越窄;当输入为中间电平时,输出码流的逻辑"0"和逻辑"1"的数量基本相同。如下图所示。

当输入增大时,当调制器输出逻辑"0"时,输入减去反馈值(-V_{ref}),会变得更大,使得积分器内部值的增加速度变快,从而缩短输出逻辑"0"的时间;当调制器输出逻辑"1"时,输入减去反馈值(V_{ref}),由于输入值较大,相减后的绝对值较小,因此积分器内部值的减小速度变慢,从而延长输出逻辑"1"的时间;输入减小时同理,最终体现为输出逻辑"0"的时间延长,输出逻辑"1"的时间变短。

3.CIC滤波器结构及工作原理

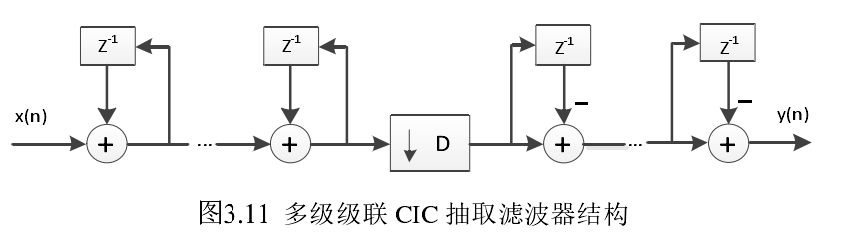

CIC抽取滤波器基本结构如图所示:由积分器、降采样抽取器和梳状器构成。

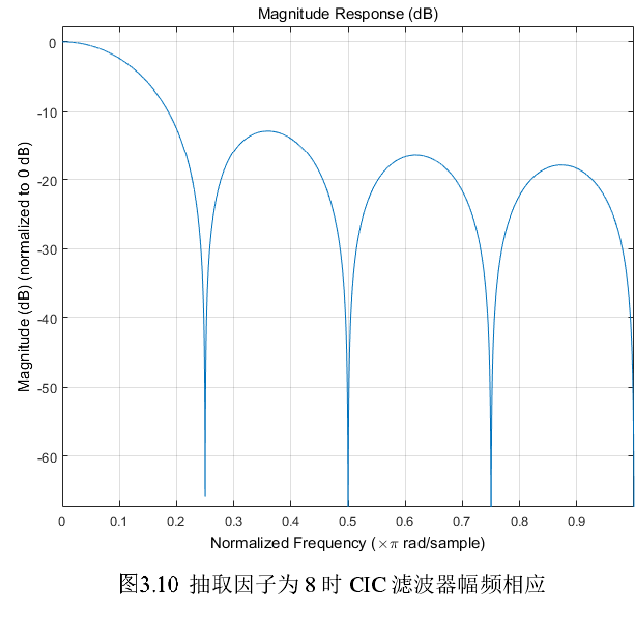

一级CIC滤波器的幅频响应曲线如下图所示,可见其通频带在低频段,因此可以视为低通滤波器。

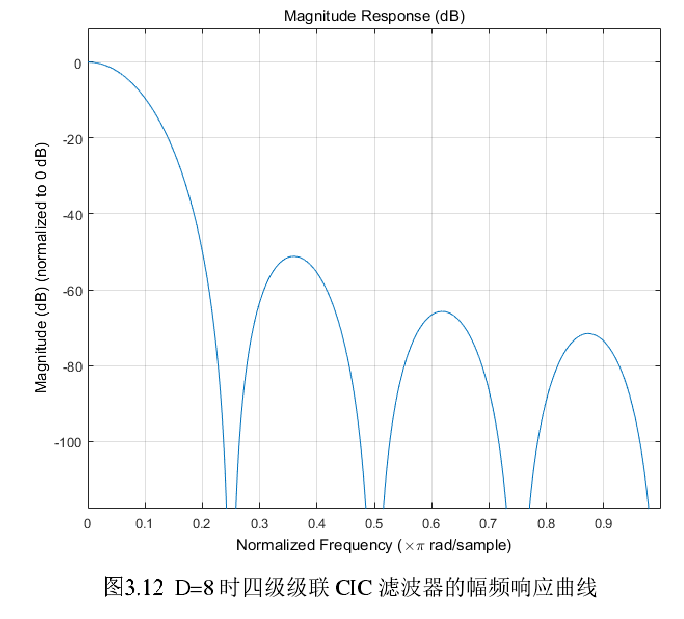

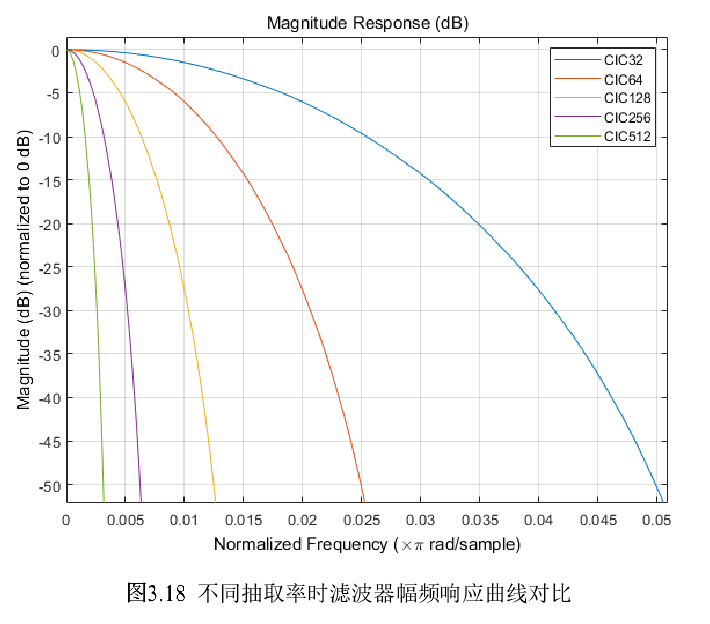

CIC滤波器的幅频响应与CIC滤波器级数以及抽取系数(降采样的倍数)有关。级数提高会提高阻带的衰减,但同时也会使得通带的下降幅度变大,因此级数需要根据实际需求去选取。

抽取系数的提高会使得CIC滤波器通频带内的信号衰减变得更加剧烈。

∑-Δ调制器输出的高频一位码流通过低通滤波器后便会被转换为多位量化值。如果将调制器的输出的码流视为PWM波,将逻辑"1"占一次转换输出的逻辑值的比例视作占空比,由于低通滤波器的截止频率低于方波的一次谐波频率时,方波便会被只保留直流成分,此时占空比大的PWM波所具有的能量更大,因此也会被转化为高幅度的直流量;占空比小的PWM波会被转化为低幅度的直流量,从而实现一位码流到多位量化值的转变。

4.参考资料

吴迪. 一种Sigma-Delta ADC中数字抽取滤波器的设计[D].西安电子科技大学,2020.

https://www.bilibili.com/video/BV1PV41127QD

https://zhuanlan.zhihu.com/p/88692450

https://en.wikipedia.org/wiki/Cascaded_integrator–comb_filter

https://blog.csdn.net/qq_41332806/article/details/108859496