1. Configuration

-

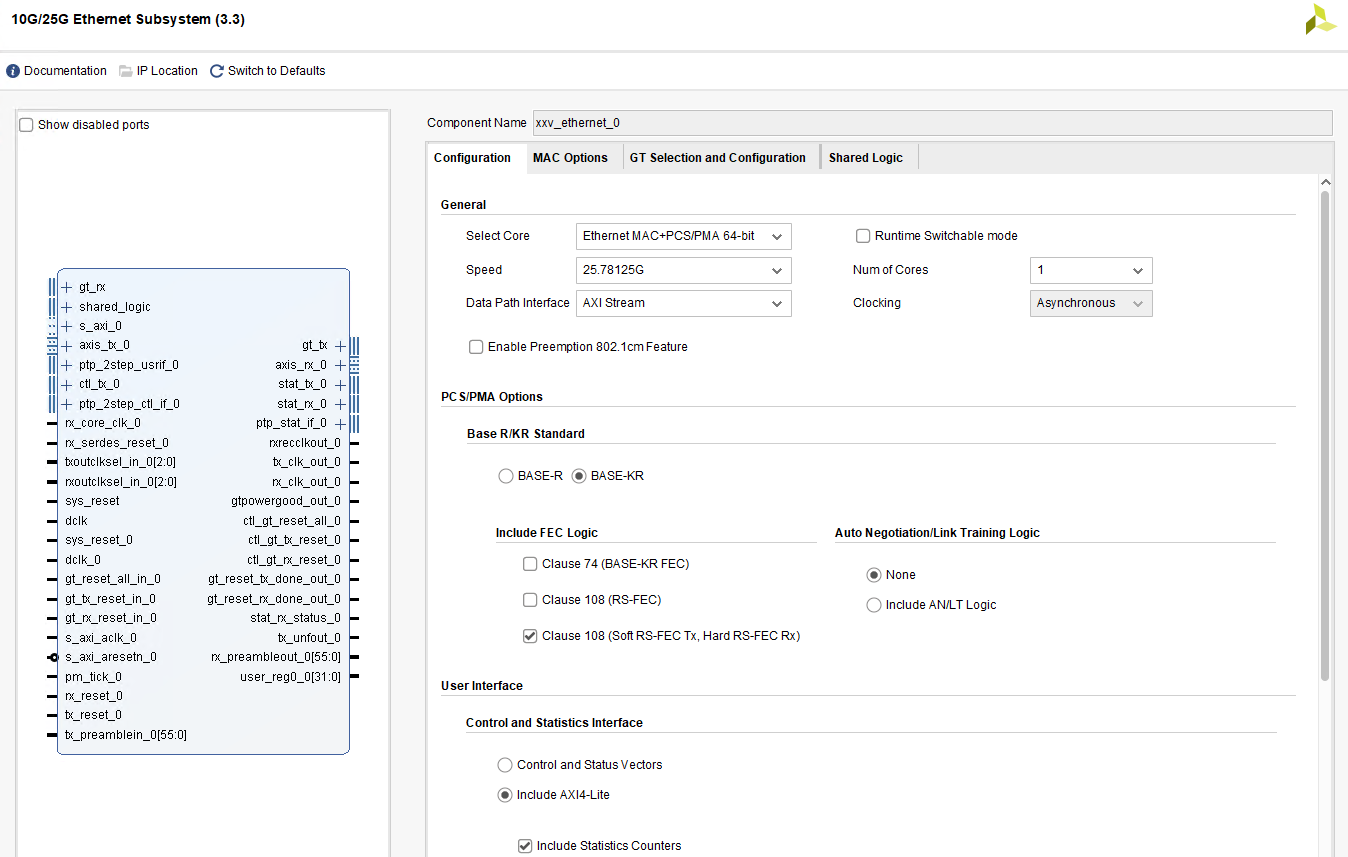

General选项卡

select core 有多种架构方式,我选择Ethernet MAC + PCS/PMA;

速度可接口就不同多说;

-

PCS/PMA Options

Base R/KR Standard:Base-R和Base-KR 是两种以太网物理层接口标准。在IEEE 802.3 有详细的介绍,简单的说就是定义了连接方式和编码方式。Base代表基带(编码),R代表编码方式是64R/66R,K代表背板。Base-R是走光纤,而Base-KR是串行走背板铜线。具体介绍还可以参考以下博客:

Include FEC Logic:FEC即前向纠错,过在传输码列中加入冗余纠错码,在一定条件下,通过解码可以自动纠正传输误码,降低接收信号的误码率(BER)。

Auto Negotiation/Link Training Logic:自协商相关的逻辑控制,这儿不需要。

物理层相关的结构,可以参考下图。

- User Interface

主要是配置IP Core的方式,这个比较常见,不做过多说明。

2. MAC Options

- Flow Control

流量控制选择,IEEE 802.3中有,IP core貌似能实现暂停和继续发送或接收;

- IEEE PTP 1588V2

这是个比较重要的功能,关于1588可以专门查阅文献,此处用“2步”方式,周期是4000ps,即250MHz,时钟需要自己引入;

- Datapath Parity Feature

奇偶校验,IP core 采用的是偶校验。

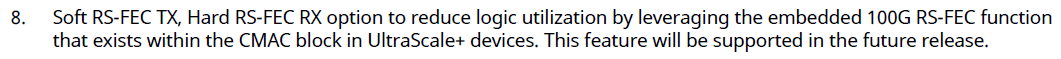

3. GT Selection and Configuration

这个选项卡中主要是配置GT口。

- GT Clocks

配置GT口的参考时钟和动态配置时钟Dynamic Reconfiguration Port (DRP)。

- Core to GT Association

选择实际GT口的位置,这与实际的布板有关;

- Advanced Options

这里面比较重要的就是插损(RX Insertion Loss at Nyquist),数值与实际的硬件设计有关。

4. Shared Logic

这个选项比较常见,主要涉及到example或者移植的时候,时钟。复位等公共的逻辑放在哪里的问题,不用多说。

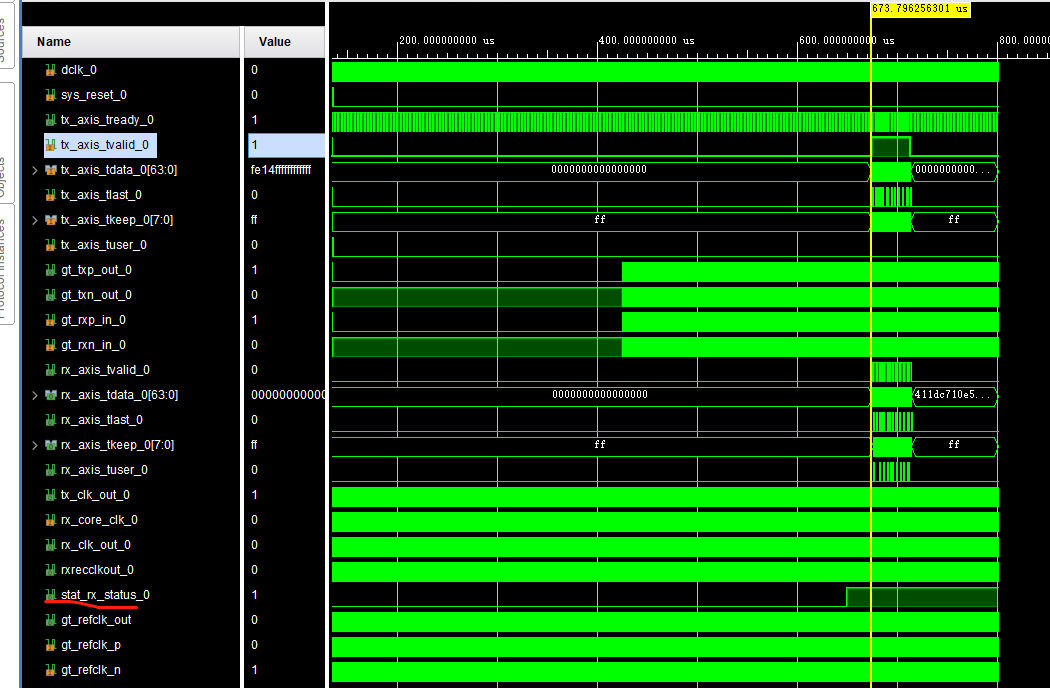

仿真

IP core生成之后,打开Example 工程,可以进行回环数据仿真测试,比较慢(据说代码中增加宏定义SIM_SPEED_UP 可以提高仿真的速度,好像差不多),大约需要仿真到接近700us时才能看到回环数据。

PS:一开始以为GT口有数据,以为是回环数据,但是发现用于端的axi总线上还没发数据,后来咨询才得知:SerDes设备(GT口)上电后总线上一般都有数据传输,即使没有数据传输需求也会传送IDLE码。所以这些数据是IDLE码。

参考文献

IEEE802.3-2015 Cl74 BASE-R PHY的前向纠错(FEC)子层 等部分相关点翻译_Apollon_krj的博客-CSDN博客