TRM手册中给出了所有的寄存器配置,在 slave fifo模式或者 GPIF模式等,所以对于用到的各种寄存器配置需要查看此手册,当然还可以配合着应用手册《AN61345》.

1.主机操作

对于USB2.0的设备来说,是不能作为主机,主动发送数据或者接收数据的,如下面的描述。

OUT意味着 主机到设备,IN是设备到主机,这里注意以下,若是工作在slave fifo模式下,FPGA与 EZ-USB通信,最后传递给上位机,应该是工作在IN模式(输入模式)。

OUT意味着 主机到设备,IN是设备到主机,这里注意以下,若是工作在slave fifo模式下,FPGA与 EZ-USB通信,最后传递给上位机,应该是工作在IN模式(输入模式)。

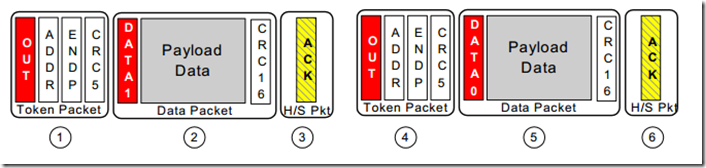

3.事务处理方式

令牌包,数据包,握手包。

(1)首先是主机发送 get descriptor device指令请求给地址0;

(1)首先是主机发送 get descriptor device指令请求给地址0;

(2)设备响应请求,发送ID给主机得到确认;

(3)主机发送地址请求,此地址是设备特有的;

(4)主机再发送其他额外的设备信息get descriptor device;

其实上述的这些响应,EZ-USB内部会自动完成,只需了解其机制即可。

4.1重枚举

当第一次插入设备,需要安装驱动,等下次再插入设备时,会自动被识别,这就是重枚举过程。

5.EZ-USB架构

手册中有介绍,ENDPOINT buffer一共就有12种配置方式,如下所示:

对照两个图可以看出,端点缓冲区的设置是与CPU部分进行通信的,包括缓冲区大小,几个缓冲区,输入和输出,以及缓冲模式(bulk,control,同步模式,中断模式)

对照两个图可以看出,端点缓冲区的设置是与CPU部分进行通信的,包括缓冲区大小,几个缓冲区,输入和输出,以及缓冲模式(bulk,control,同步模式,中断模式)

7.SLRD,SLWR,FLAGABC,SLOE,SLCS几个信号讲解

上图中,FPGA与CY7C68013A进行通信,工作在slave fifo模式,其中我们只需用到FPGA对CY进行写操作。所以对于写入情况手册中有给出如下情况:

在写入数据时,是伴随着ifclk时钟频率下,在上升沿进行采样,且此时SLWR为低电平,SLCS为低电平。

在写入数据时,是伴随着ifclk时钟频率下,在上升沿进行采样,且此时SLWR为低电平,SLCS为低电平。

flagABC,其中A代表空,B代表满,C代表可编程,FPGA可以通过这几个信号来判断CY是写满还是读空。

SOLE是输出使能信号,高电平使能。

SLRD是读出信号,如下图所示:

SLRD也是低电平有效,并且SLCS金额SLOE也是低电平时在ifclk时钟频率下开始读出数据,由于FPGA与CY通信只是写入情况,用不到读出,所以可以直接将SLOE,SLRD直接拉高。

SLRD也是低电平有效,并且SLCS金额SLOE也是低电平时在ifclk时钟频率下开始读出数据,由于FPGA与CY通信只是写入情况,用不到读出,所以可以直接将SLOE,SLRD直接拉高。

8.电源管理模式

主要有suspend,resume,idle,wakeup模式

8.1晶振时钟源寄存器设置,默认值是1.

wakeup引脚的优先权是通过WUPOL和WU2POL来设置的,DPEN使用来设置D+的使能,WUEN使能wakeup引脚,WU2EN使能WU2引脚。通过设置上述参数,就可以进入到wakeup中断。有上述可以看出,有三种中断源可以使CY进入到中断模式,1)wakeup(WUEN),2)D+(DPEN),3)WU2(WU2EN),进入中断后,8052就会推出idle模式。

wakeup引脚的优先权是通过WUPOL和WU2POL来设置的,DPEN使用来设置D+的使能,WUEN使能wakeup引脚,WU2EN使能WU2引脚。通过设置上述参数,就可以进入到wakeup中断。有上述可以看出,有三种中断源可以使CY进入到中断模式,1)wakeup(WUEN),2)D+(DPEN),3)WU2(WU2EN),进入中断后,8052就会推出idle模式。

9.复位

复位有三种方式:硬件复位(低电平有效),CPU复位(由EZ-USB的逻辑控制),USB总线复位。

复位有三种方式:硬件复位(低电平有效),CPU复位(由EZ-USB的逻辑控制),USB总线复位。

10.端点介绍

对于每个buffer缓冲器的数据大小通过以下寄存器进行设置 。

11.自动指针

自动指针会当每个字节发送过来后自动增加。

其他参看博客连载18的内容