计算机组成有三个部分:中央处理单元,主存储器,输入/输出

- 中央处理单元(cpu)

中央处理单元用于数据运算。在大部分体系中又分为算术逻辑单元,控制单元,寄存器(快速存储单元)- 算术逻辑单元

算术逻辑单元对数据进行逻辑,移位和算术运算 - 寄存器

期存器是用来临时存放数据的高速独立的存储单元,寄存器又分为数据寄存器,指令寄存器,程序计数器 - 控制单元

控制单元控制各个子系统的操作,我的理解就是一个大型的信息交换的场合。

- 算术逻辑单元

- 主存储器

主存储器是存储单元的集合,说白了就是硬盘等一切可以进行存储的总和。每一个存储单元都有地址,所有的存储单元的标识地址的总数称为地址空间。由于计算机的存储的原因,地址是以二进制整数的形式存在在电脑中的。

存储器又分为RAM和ROM

RAM是计算机的主存中重要组成部分,RAM和ROM的区别在于,前者可以通过写入不断覆盖,并且如果断电的话,这一部分信息并不会保存,对应的是电脑中内存-

随机存取存储器(RAM)

RAM分为SRAM(静态)和DRAM(动态),SRAM通电的时候数据始终存在,不需要刷新,速度快,价格高

DRAM内存需要周期性刷新,速度慢,比较便宜,价格相对较低 -

只读存储器(ROM)

ROM切断电源后数据也不会丢失,用来存储程序和程序所产生的数据

PROM:可编程只读存储器

EPROM:可编程可擦除的只读存储器

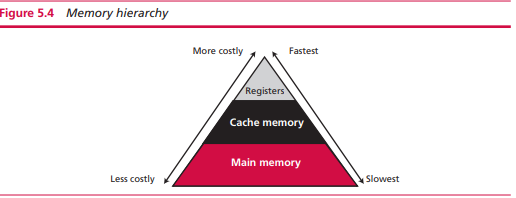

EEPROM:电科擦除的可编程只读存储器 - 存储器的层次结构

计算机需要用到很多存储器,不同的需求对应不同性能的存储器。

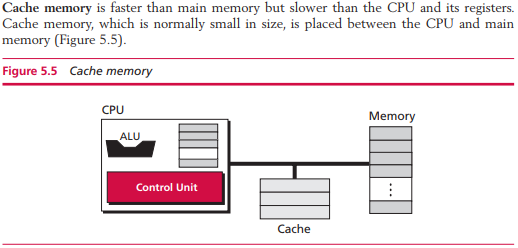

- 高速缓冲存储器

存取速度比主存快,但是比CPU内部的寄存器慢。每次CPU存取主存中的一个字时,都要先询问缓存,如果存在,就直接从缓存复制,如果不存在,就从主存中复制一份,并且覆盖到缓存

-

-

输入/输出子系统

输入/ 输出子系统可以使计算机与外界通信。,并且在断电的时候也能保存数据,分为存储设备和非存储设备-

非存储设备

鼠标,键盘,打印机等 - 存储设备

就是我们常说的硬盘之类的,但是书中这个存储设备的概念特别广,包括以前使用的光盘等都属于存储设备。

-

- 子系统的互连

- CPU和存储器之间的连接

CPU和内存之间有三组统称为主线的线路连接在一起,分别为数据总线,地址总线和控制总线- 数据总线:由多根线组成,每根线上每次传输一位数据,线的数量取决于字的大小,如果计算机是64位的,那么就需要64根线。

- 地址总线:允许访问存储器中的某个字,取决于存储空间的大小。

- 控制总线:控制总线负责在中央处理器和内存之间传送数据

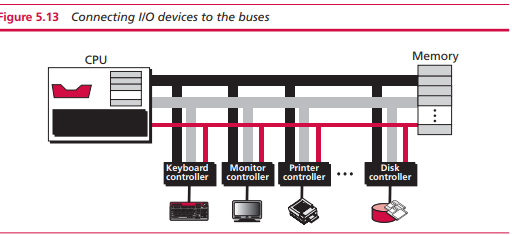

- I/O设备的连接

输入/输出设备不能够直接跟总线相连,如下图

因为这些设备并一定是电子设备,比如早年使用的光盘。但是CPU和存储器都是电子设备,必须要有一个中介来处理这种差异。输入/输出控制器就扮演这一角色

控制器:类似于接口,控制器可以串行或者并行连接设备。- SCSI

小型计算机系统接口,是一个8位,16位,32位的并行接口,连接器的两端都必须有终结器,并且,每个设备都必须有唯一的地址。

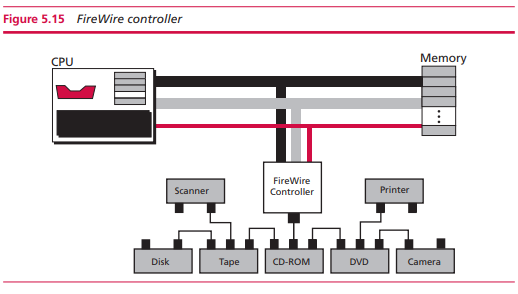

- 火线

高速的串行接口,不需要终端数据采用包的形式。

- USB

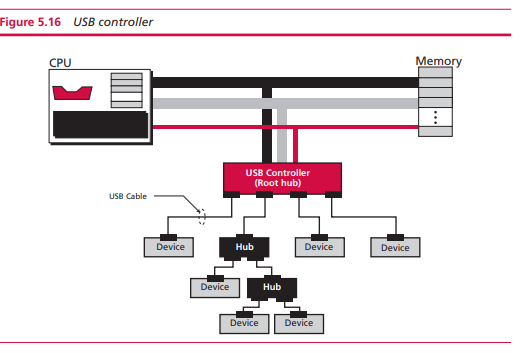

通用串行总线用以连接高速和低速设备。这个接口可以允许多个设备以树状拓扑结构连接到一个控制器上(usb根集线器),还有集线器负责连接更多的设备,集线器作为树的节点不能感知到其他集线器,控制器能够感知到所有的节点。除此之外,

这个接口还支持热插拔,即插即用。

- SCSI

-

输入/输出设备的寻址

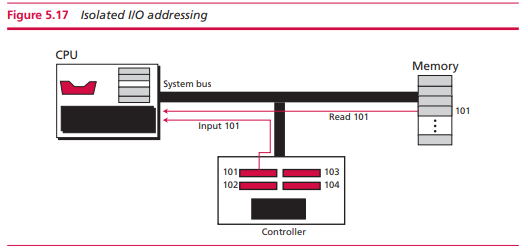

CPU使用同一根数据总线在内存和i/o设备之间传输数据,计算机用指令区分,如果指令涉及到内存,就找内存,如果涉及到输入输出设备就找对应的设备。为io设备寻址分两种,一种io独立寻址,一种io存储器映射寻址-

io独立寻址

用来读写内存和读写io设备的指令区分开,每个输入输出设备都有自己的独立地址。

-

io存储器映射寻址

把每一个io设备中的寄存器看成内存中的某个字,命令不做区分,把地址写入到内存中。

-

- CPU和存储器之间的连接

-

程序的执行

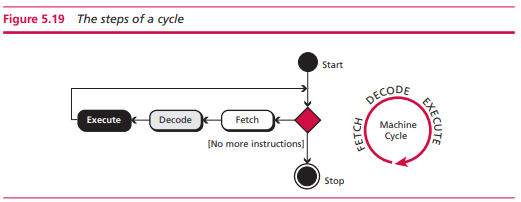

计算机通过程序来处理数据,而程序其实就是一系列的指令- 机器周期

CPU利用重复的机器周期执行程序中的指令,一个机器周期包括三个步骤:取指令,译码,执行

取指令:控制单元把下一条要执行的命令拷贝到CPU的寄存器上,并且这个指令的地址复制到计数器中。

译码:控制单元将指令译码为计算机可以执行的二进制代码

执行:控制单元发送任务命令到CPU的某个部件(视情况而定,如果是计算,就通知计算逻辑单元,如果只是存取就通知内存)

- 输入/输出操作

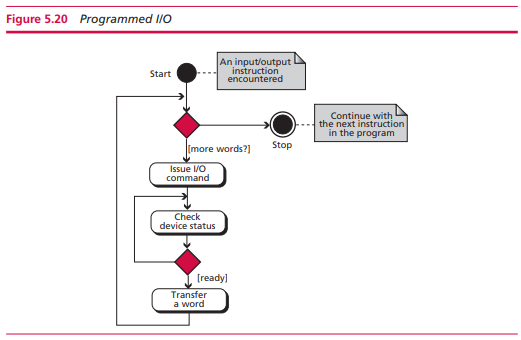

之前提到因为io设备不一定是电子设备,所以,传输速度比CPU要慢的多,CPU在某种程度上必须和io设备同步。有三种方法实现这种同步- 程序控制输入/输出

这种方法是CPU采用轮询的方式不断的查询io设备的状态,如果io设备准备好数据了就开始传输

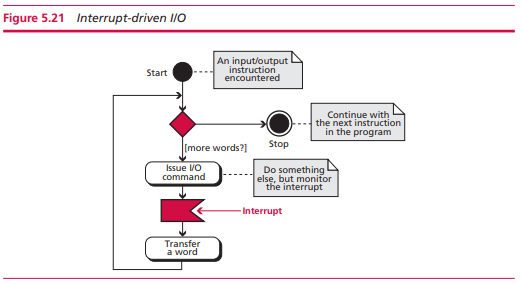

- 中断控制输入/输出

这种方式当io设备准备好的时候,它会中断CPU,在这之前,CPU都可以在运行别的程序

-

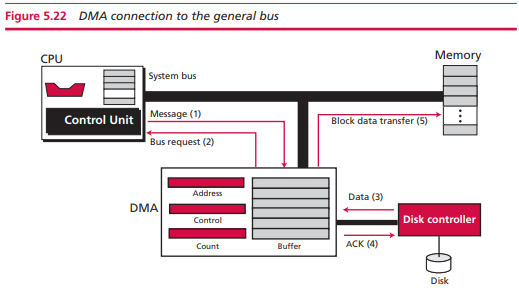

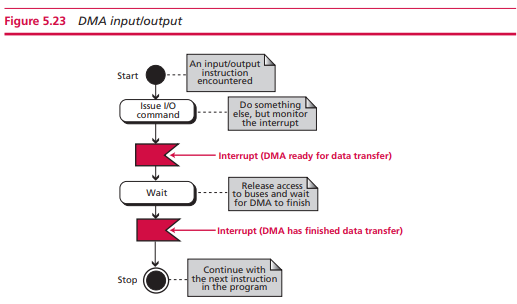

直接存储器存取

这个方法可以在高速io设备间传输大量的数据块,他的原理是增加一个DMA的类似CPU的硬件,它是一个控制器,开始的时候,CPU会发送一些传输的基本信息如传输的类型,内存的地址等,当准备好传输的时候,由DMA获取到总线的使用权,这时候CPU是停止工作的。这时候才真正传输数据。注意的是,这种方法的有点在于快,因为重新增加了一个硬件设施。

- 程序控制输入/输出

-

不同的体系结构

CISC:复杂指令集计算机的缩写。CISC架构是使用非常多的复杂的指令,每一个简单或者复杂的任务都有相对应的指令,虽然在这种体系下设计程序语言会相对容易一些,但是使得硬件设施非常复杂,但是设计者提出一个解决方案,CPU不直接执行指令,而是执行称为微操作的指令,把原本复杂的指令翻译成简单操作,这又需要被称为微内存的架构支持。微内存负者记录每一个复杂指令的微操作,使用微操作的程序设计语言被称为微程序设计(上次有在微博上看到好像win10使用的就是这个架构)

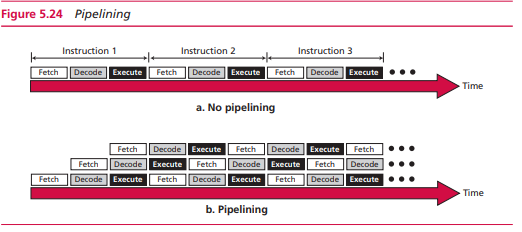

RISC:精简指令集计算机的缩写,和CISC相反,他使用的非常简洁的指令,每一个复杂的指令都是由简单指令进行模拟的。 - 流水线

计算机使用流水线的技术改善指令的周期的运行效率,每一条指令都需要进行三个周期,控制单元如果能够同时执行两个或者三个阶段,那么下一条指令就可以在前一个指令的第二阶段运行了。如图:

-

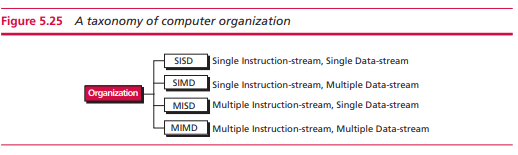

并行处理

随着技术的进步,一台计算机里可能有多个控制单元和多个算计逻辑单元,多个内存单元。所以诞生了并行处理这个思想,并行处理涉及不同的技术,把这个技术分为四个分类

-

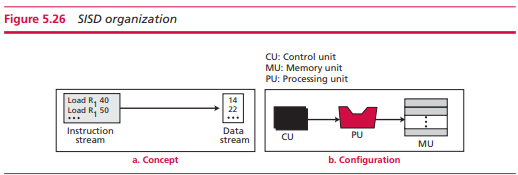

SISD:单指令流,单数据流,意思就是只有一个算术逻辑单元,一个控制单元,一个内存。一个指令对应的一个内存中多个数据项

-

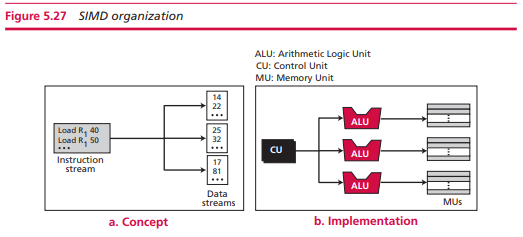

SIMD:单指令流,多数据流,计算机内部有一个控制单元,但是有多个算术逻辑单元,多个内存单元。早起的处理器基本都属于这一种,看到这个模型的时候,想起以前在课上问操作系统老师,并行的问题,他说虽然CPU可以有多个,但是出口只有一个,这个出口应该就是这个指令流吧

-

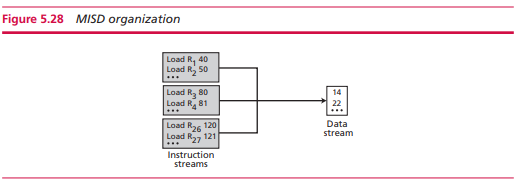

MISD:多指令流,单数据流,这个架构其实效率没有MIMD高,所以没有被实现过。本身也很奇怪吧。多个指令,就一个数据流,等于就一个干活的

-

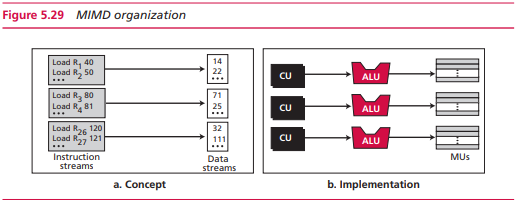

MIMD:多指令,多数据流。多个指令应用于多个数据流。一般在这种架构上,内存是共享的。

-

- 机器周期